# Wireless HDL Toolbox™ User's Guide

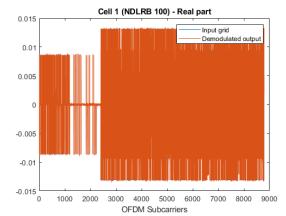

# MATLAB&SIMULINK®

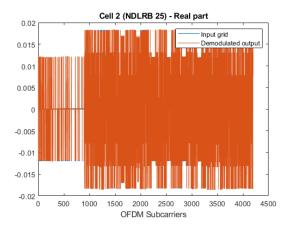

R

**R**2021**a**

# **How to Contact MathWorks**

Latest news:

Phone:

www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

$\searrow$

508-647-7000

#### The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

Wireless HDL Toolbox<sup>™</sup> User's Guide

© COPYRIGHT 2017 - 2021 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ {\tt products}\ {\tt are}\ {\tt protected}\ {\tt by}\ {\tt one}\ {\tt or}\ {\tt more}\ {\tt U.S.}\ {\tt patents}.\ {\tt Please}\ {\tt see}\ {\tt www.mathworks.com/patents}\ {\tt for}\ {\tt more}\ {\tt information}.$

#### **Revision History**

| September 2017<br>March 2018<br>September 2018<br>March 2019<br>September 2019 | Online only<br>Online only<br>Online only<br>Online only<br>Online only | New for Version 1.0 (Release 2017b)<br>Revised for Version 1.1 (Release 2018a)<br>Revised for Version 1.2 (Release 2018b)<br>Revised for Version 1.3 (Release 2019a)<br>Revised for Version 1.4 (Release 2019b)<br>Devised for Version 2.0 (Release 2020c) |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 2019<br>March 2020                                                   | Online only<br>Online only                                              | Revised for Version 1.4 (Release 2019b)<br>Revised for Version 2.0 (Release 2020a)                                                                                                                                                                         |

| September 2020                                                                 | Online only                                                             | Revised for Version 2.1 (Release 2020b)                                                                                                                                                                                                                    |

| March 2021                                                                     | Online only                                                             | Revised for Version 2.2 (Release 2021a)                                                                                                                                                                                                                    |

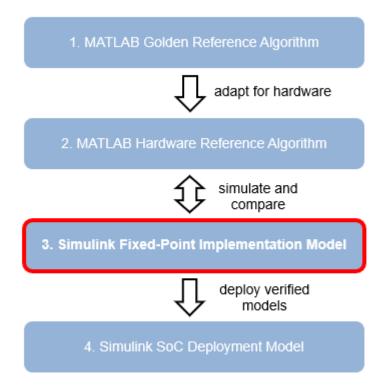

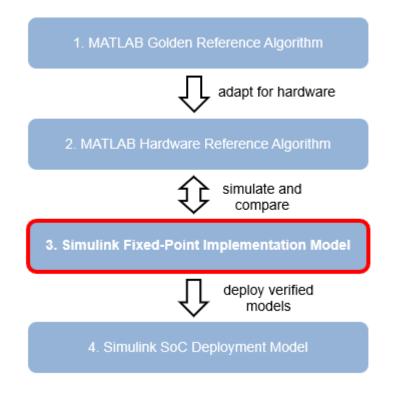

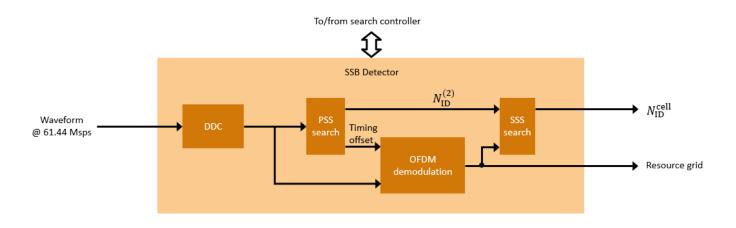

# **Model Architecture**

| Streaming Sample Interface         What Is a Streaming Sample Interface?         How Does a Streaming Sample Interface Work?         Why Use a Streaming Sample Interface?         Sample Stream Conversion         Timing Diagram of Serial Sample Interface         Using the nextFrame Output Signal | 1-2<br>1-2<br>1-2<br>1-2<br>1-3<br>1-3<br>1-4 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Sample Control Bus       Troubleshooting:                                                                                                                                                                                                                                                               | 1-7<br>1-7                                    |

| Configure the Simulink Environment for Hardware DesignAbout Simulink Model TemplatesCreate Model Using Wireless HDL Toolbox Model TemplateWireless HDL Toolbox Model Templates                                                                                                                          | 1-8<br>1-8<br>1-8<br>1-9                      |

# HDL Code Generation and Verification

# 2

1

| HDL Code Generation Support                              | 2-2  |

|----------------------------------------------------------|------|

| HDL Code Generation Support in Wireless HDL Toolbox      | 2-2  |

| Other Blocks Supporting HDL Code Generation              | 2-2  |

| Streaming Sample Interface in HDL                        | 2-3  |

| Generate HDL Code                                        | 2-5  |

| Prepare Model                                            | 2-5  |

| Generate HDL Code                                        | 2-5  |

| Generate HDL Test Bench                                  | 2-5  |

| FPGA-in-the-Loop                                         | 2-6  |

| FIL Workflow: Framed Data from MATLAB                    | 2-6  |

| FIL Workflow: Streaming Data from MATLAB                 | 2-8  |

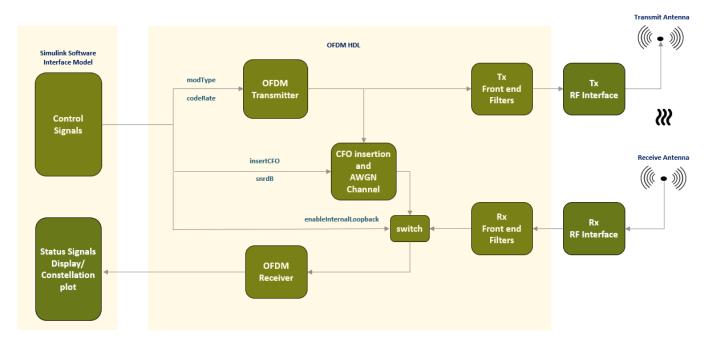

| Prototype Wireless Communications Algorithms on Hardware | 2-12 |

| How to Install Support Packages                          | 2-12 |

| Design Requirements                                      | 2-13 |

| Design for Debugging                                     | 2-13 |

| Append CRC Checksum to Streaming Data                       | 3-2  |

|-------------------------------------------------------------|------|

| Check for CRC Errors in Streaming Samples                   | 3-4  |

| Turbo Encode Streaming Samples                              | 3-6  |

| Turbo Decode Streaming Samples                              | 3-8  |

| Convolutional Encode of Streaming Samples                   | 3-11 |

| Convolutional Decode of Streaming Samples                   | 3-13 |

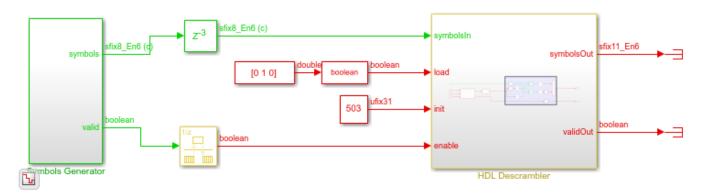

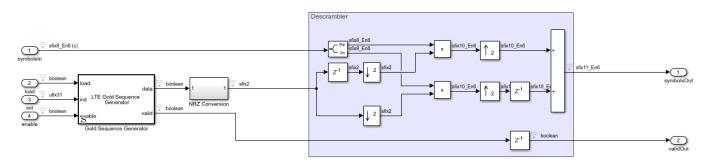

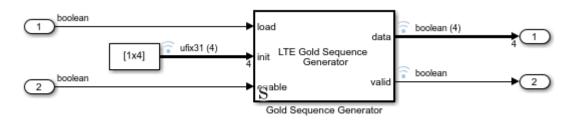

| Descrambling with Gold Sequence Generator                   | 3-16 |

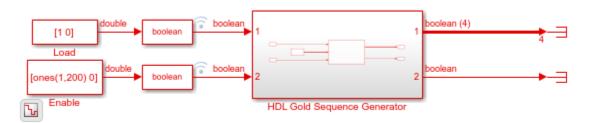

| Parallel Gold Sequence Generation                           | 3-18 |

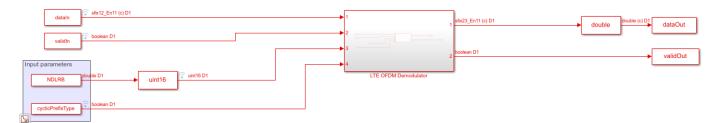

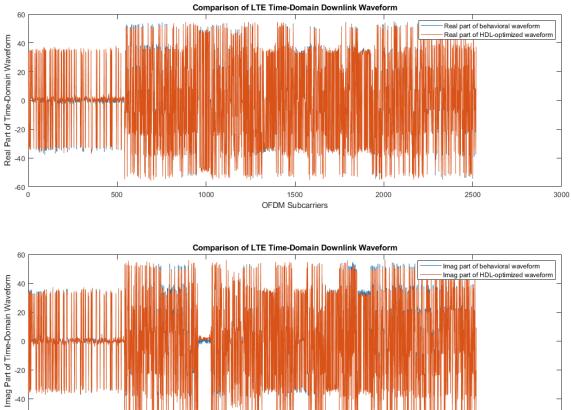

| LTE OFDM Demodulation of Streaming Samples                  | 3-20 |

| Reset and Restart LTE OFDM Demodulation                     | 3-24 |

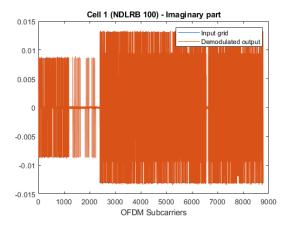

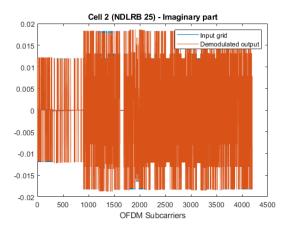

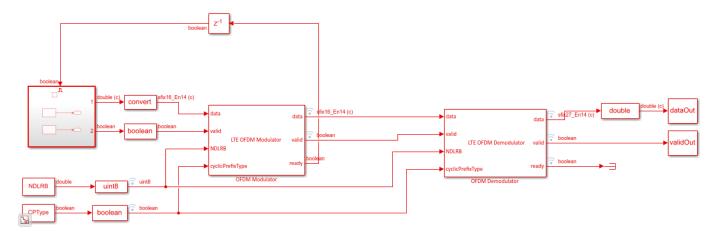

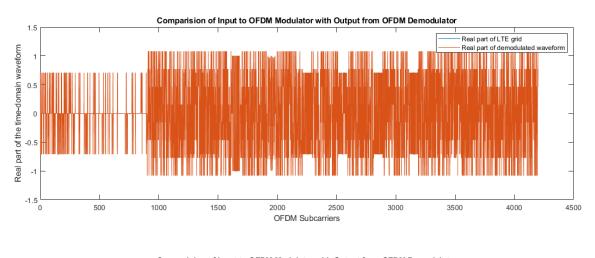

| Modulate and Demodulate LTE Resource Grid                   | 3-28 |

| OFDM Modulation of LTE Resource Grid Samples                | 3-31 |

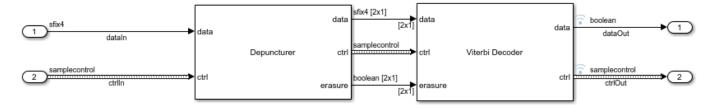

| Depuncture and Decode Streaming Samples                     | 3-34 |

| LTE Symbol Modulation of Data Bits                          | 3-38 |

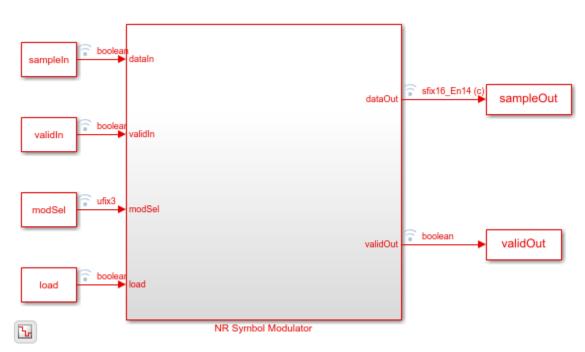

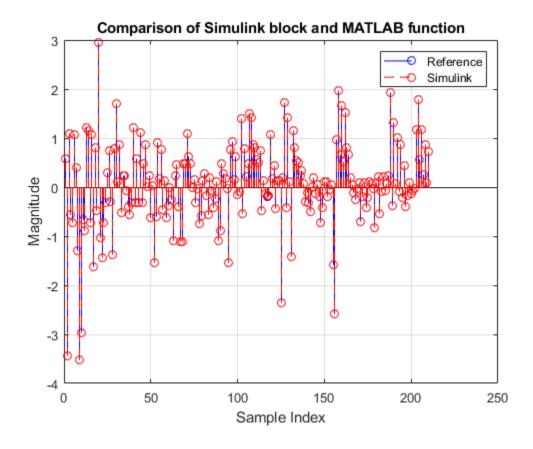

| NR Symbol Modulation of Data Bits                           | 3-40 |

| LTE Symbol Demodulation of Complex Data Symbols             | 3-42 |

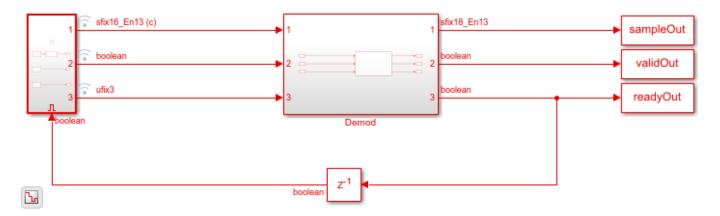

| NR Symbol Demodulation of Complex Data Symbols              | 3-45 |

| Application of FFT 1536 block in LTE OFDM Demodulation      | 3-48 |

| Convolutional Encode and Puncture Streaming Samples         | 3-51 |

| OFDM Demodulation of Streaming Samples                      | 3-54 |

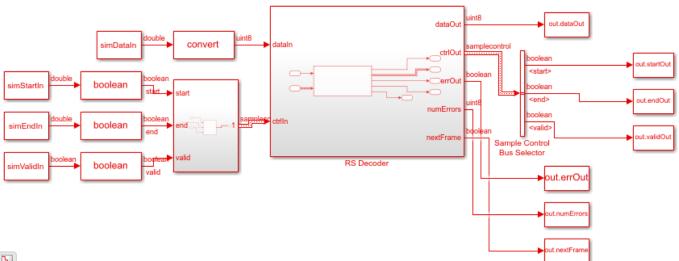

| Decode and recover message from RS codeword                 | 3-57 |

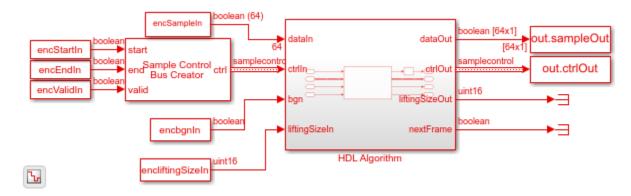

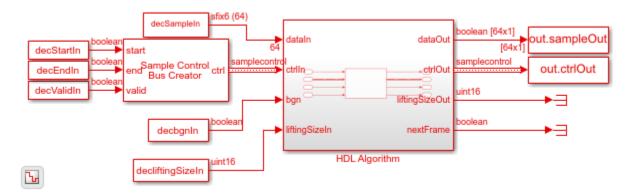

| LDPC Encode and Decode of Streaming Data                    | 3-59 |

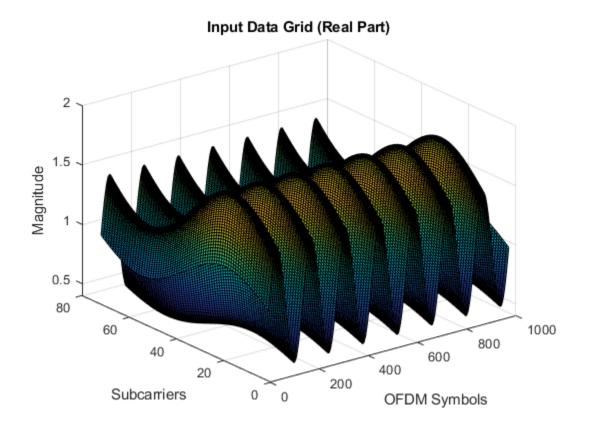

| Estimate Channel Using Input Data and Reference Subcarriers | 3-63 |

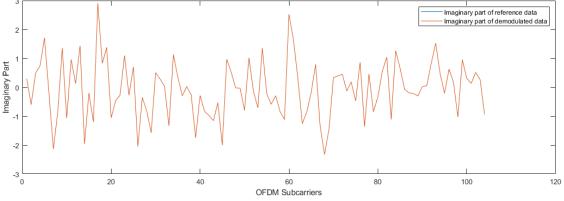

| Modulate and Demodulate OFDM Streaming Samples              | 3-71 |

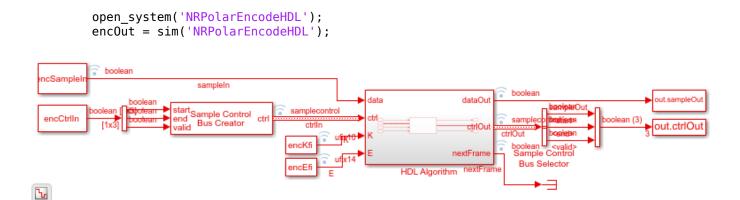

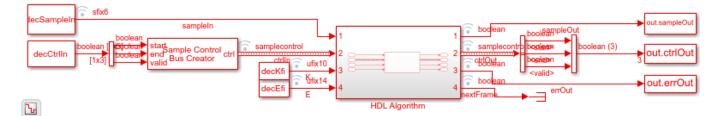

| Polar Encode and Decode of Streaming Samples                | 3-74 |

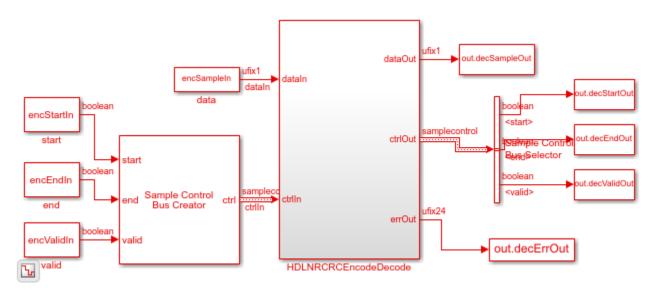

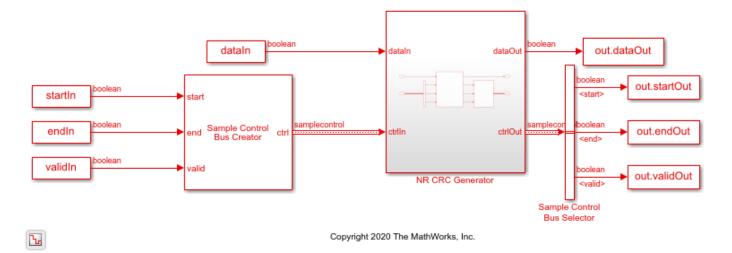

| NR CRC Encode and Decode Streaming Data                                      | 3-78 |

|------------------------------------------------------------------------------|------|

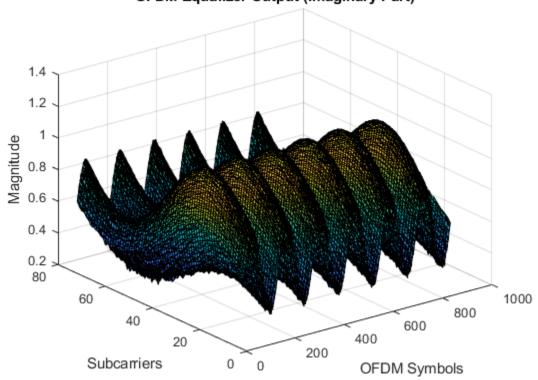

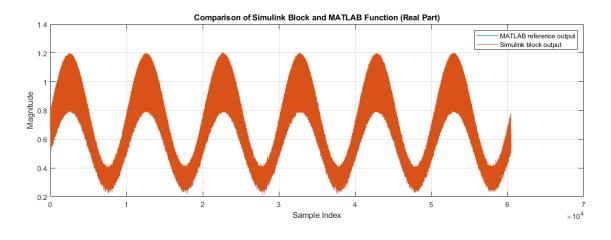

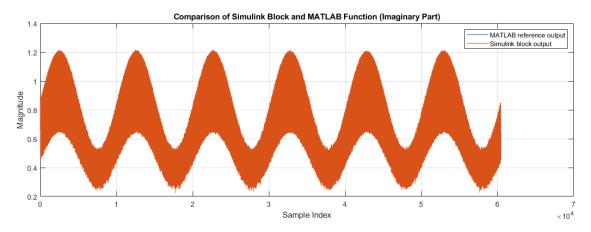

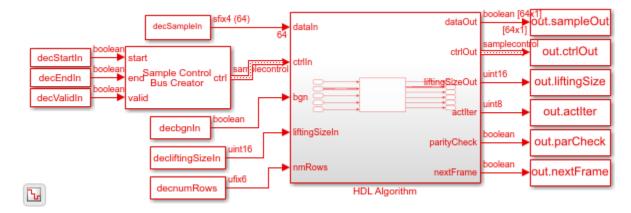

| Equalize OFDM Data Using Channel Estimates                                   | 3-82 |

| LDPC Decode Streaming Data for Multiple Code Rates with Early<br>Termination | 3-91 |

4

5

# **Featured Examples**

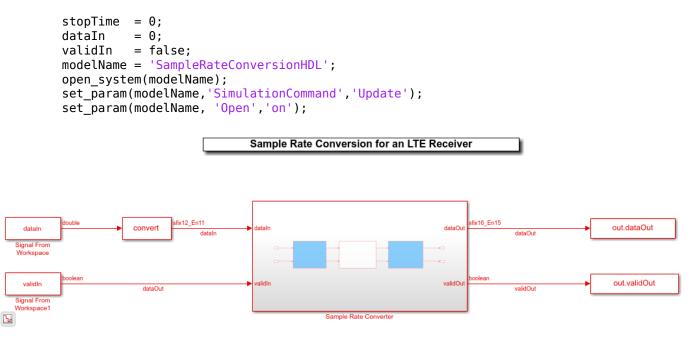

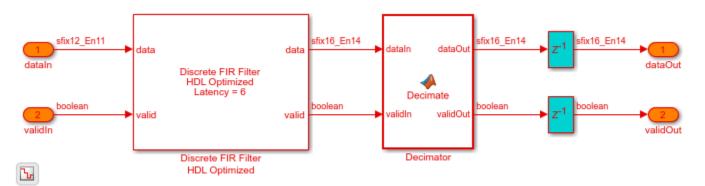

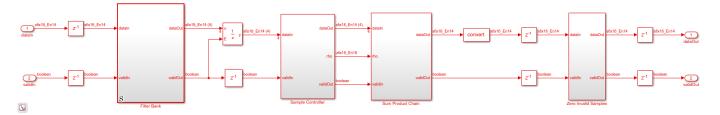

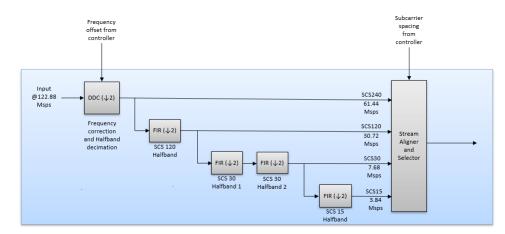

| Sample Rate Conversion for an LTE Receiver                                                  | 4-2  |

|---------------------------------------------------------------------------------------------|------|

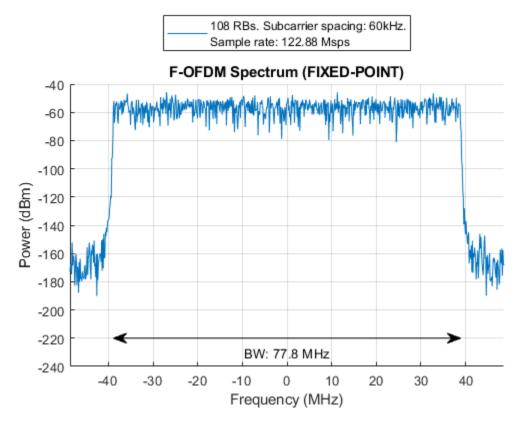

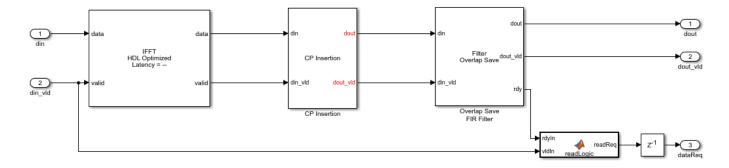

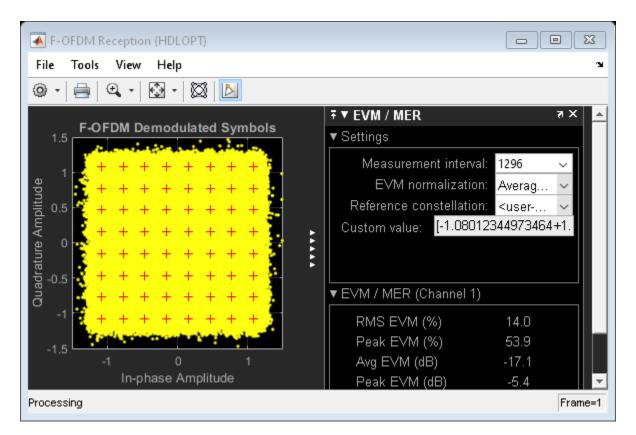

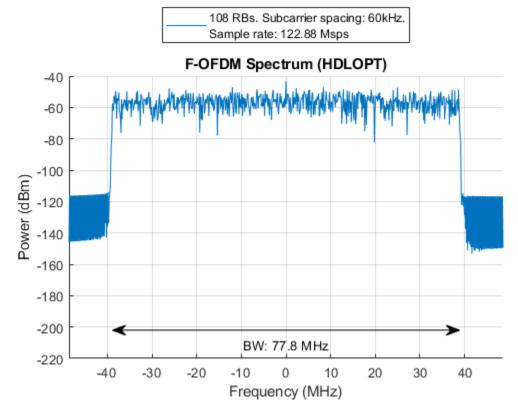

| HDL Code Generation for Filtered OFDM (F-OFDM) Transmitter                                  | 4-15 |

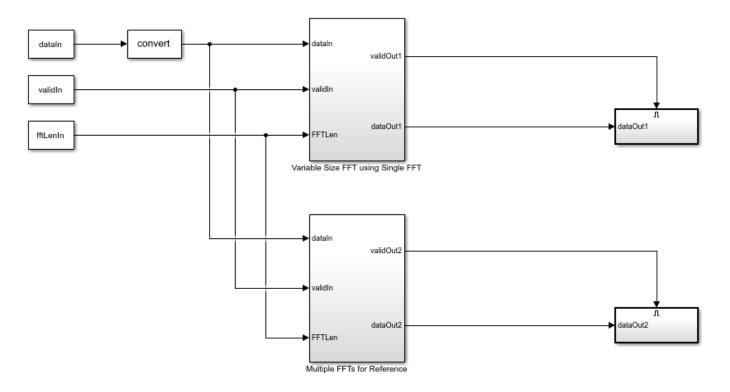

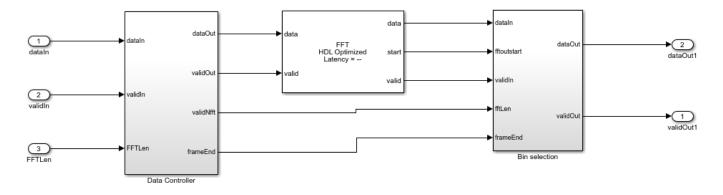

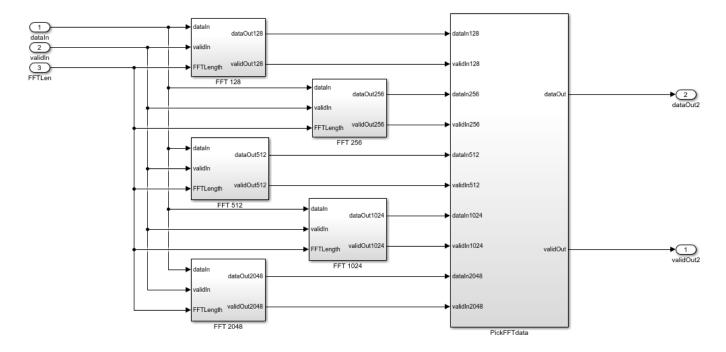

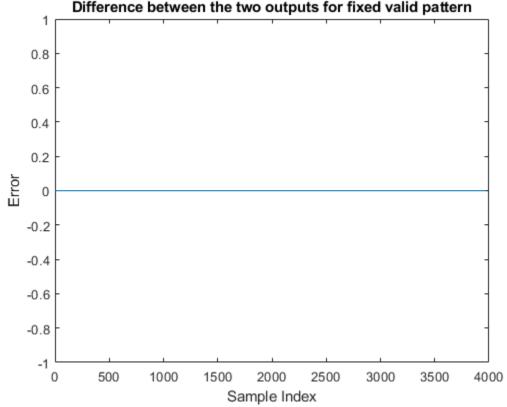

| HDL Implementation of a Variable-Size FFT                                                   | 4-25 |

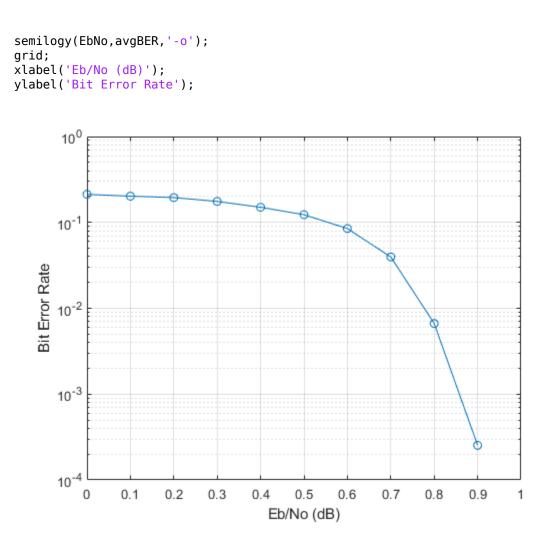

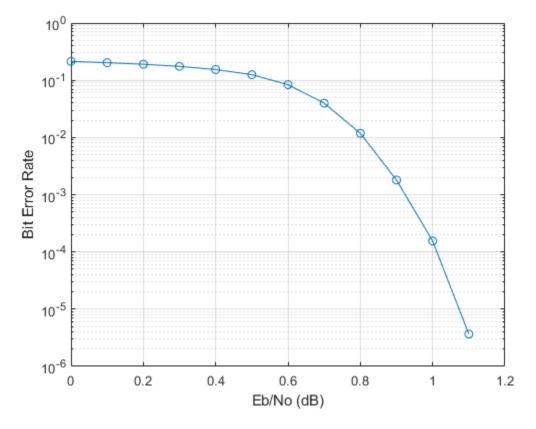

| Accelerate BER Measurement for Wireless HDL LTE Turbo Decoder                               | 4-35 |

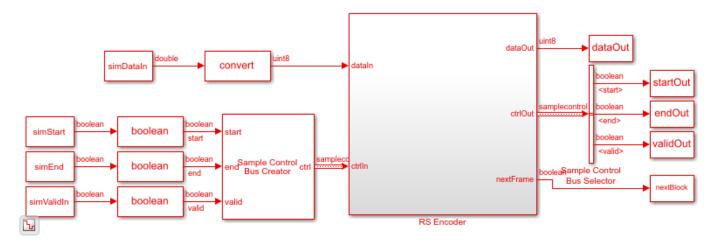

| Encode message to RS codeword                                                               | 4-41 |

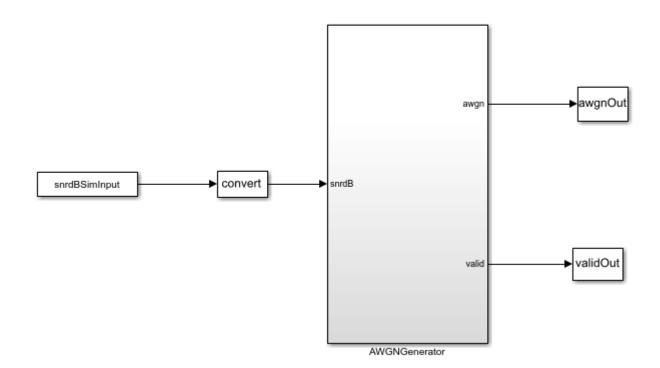

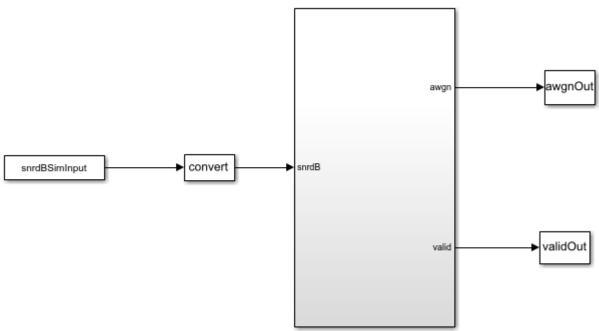

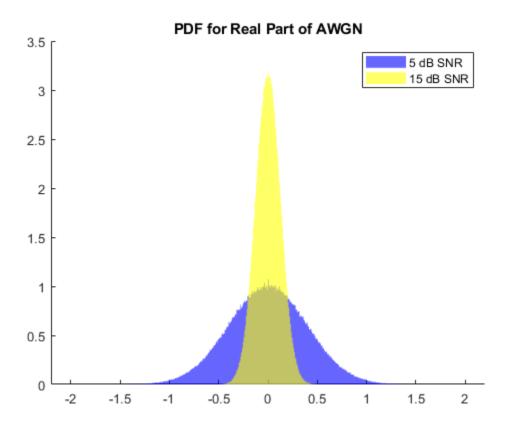

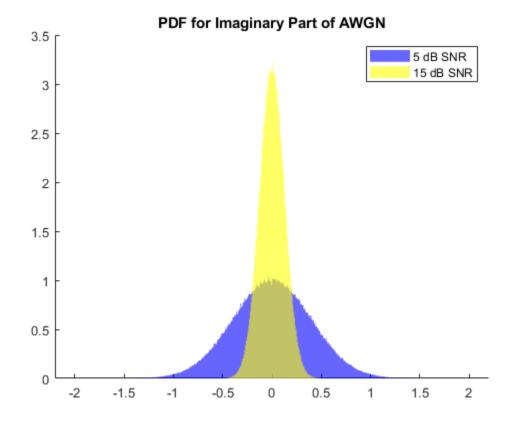

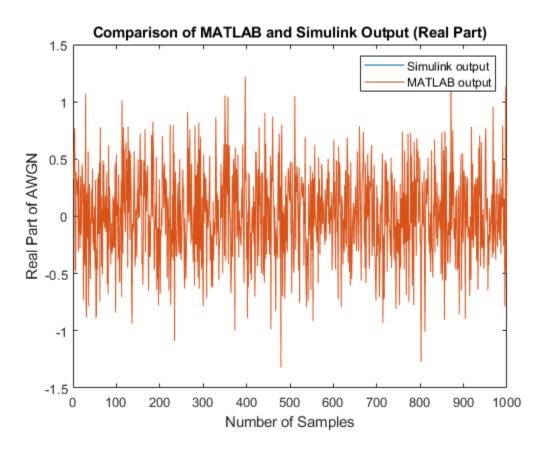

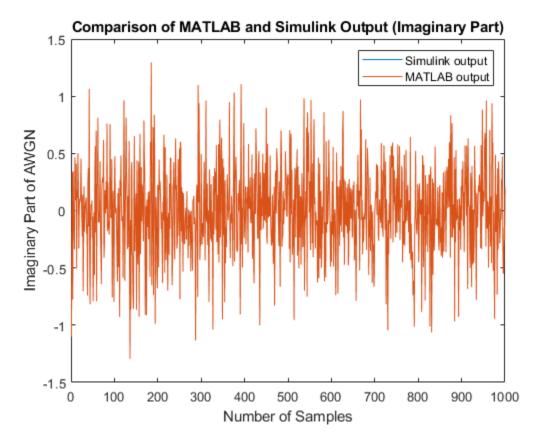

| HDL Implementation of AWGN Generator                                                        | 4-44 |

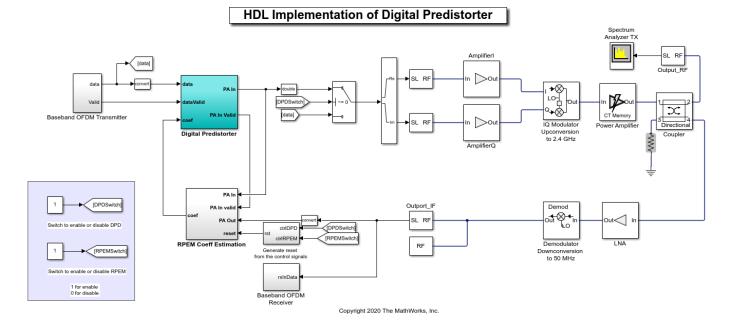

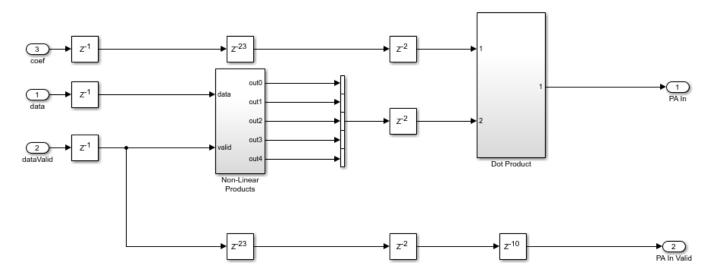

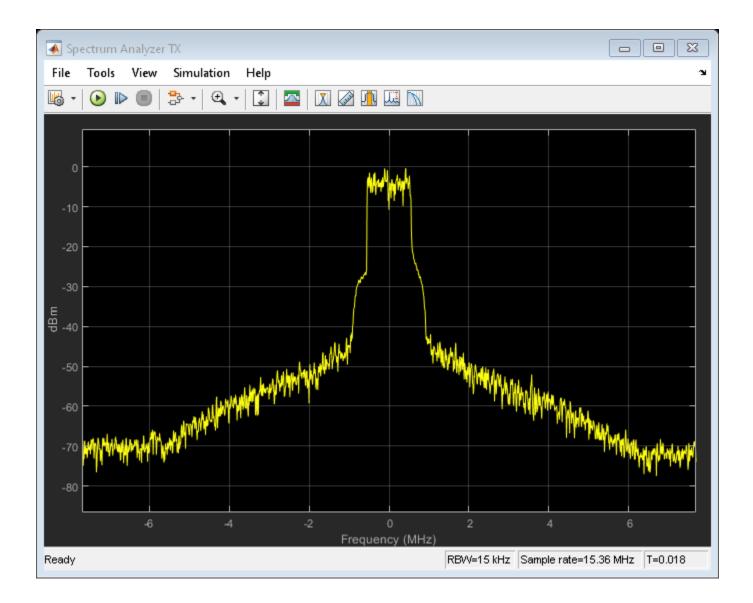

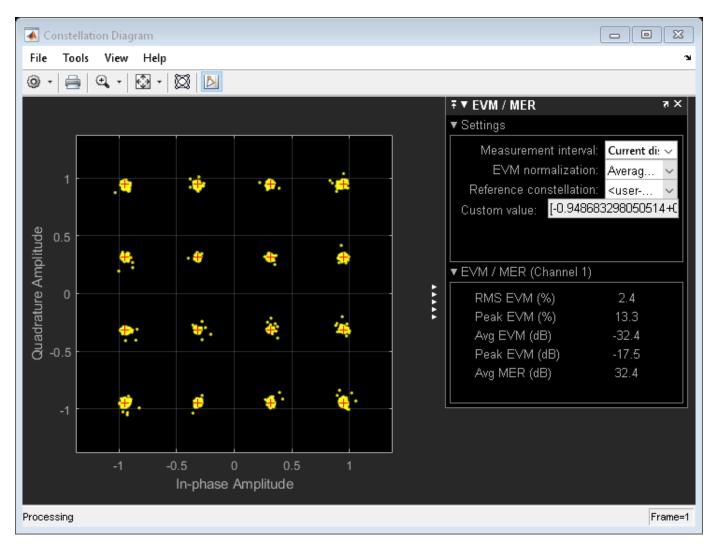

| HDL Implementation of Digital Predistorter                                                  | 4-55 |

| Encode Streaming Data Using General CRC Generator HDL Optimized<br>Block for 5G NR Standard | 4-62 |

# **Reference Applications**

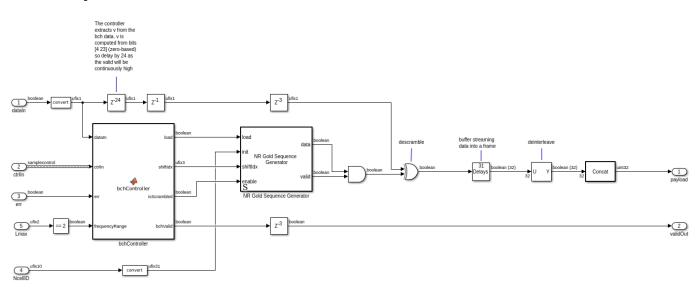

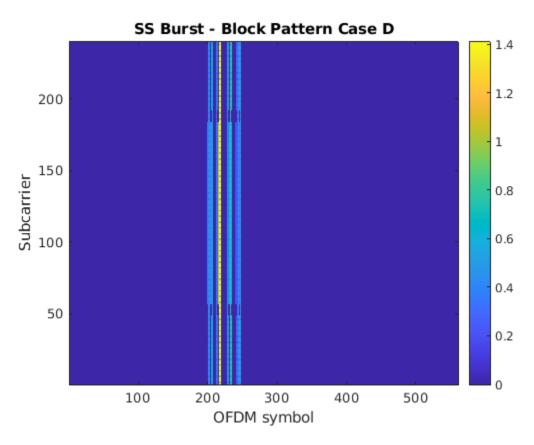

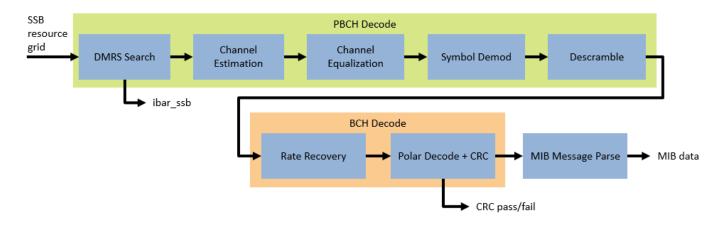

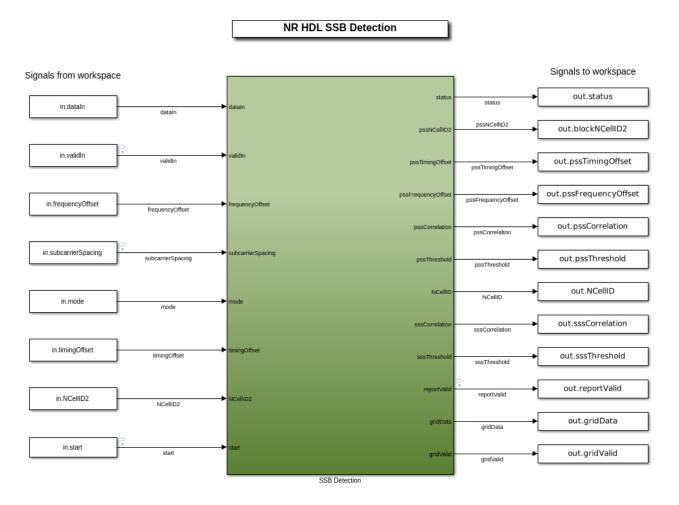

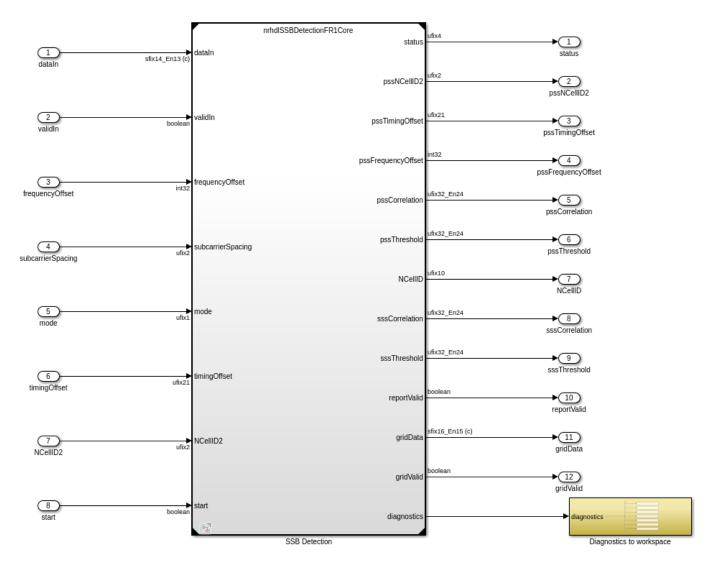

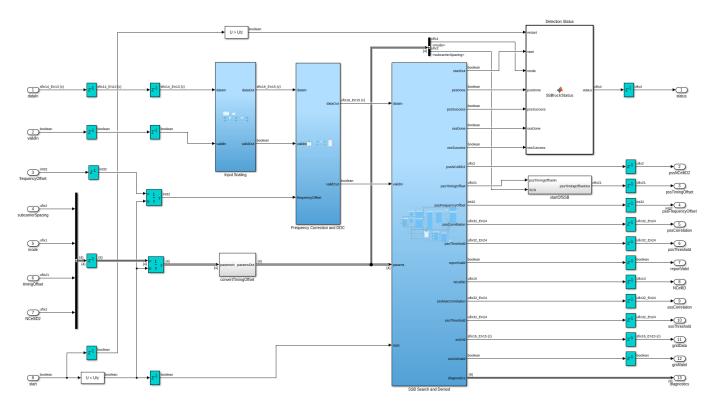

| NR HDL MIB Recovery for FR2                          | 5-2   |

|------------------------------------------------------|-------|

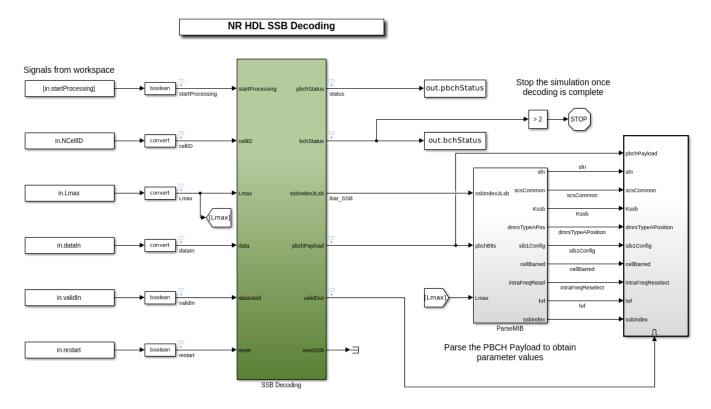

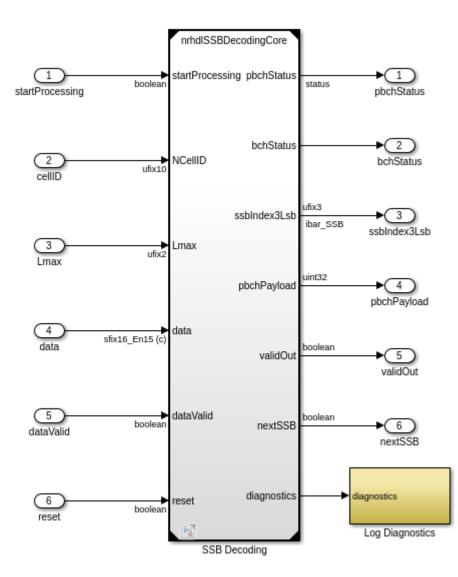

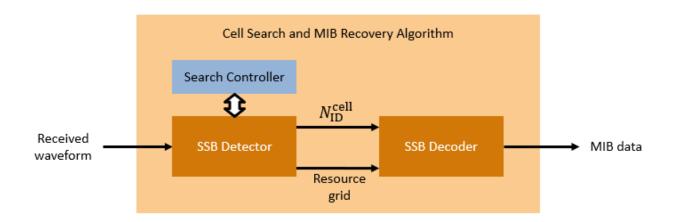

| NR HDL MIB Recovery                                  | 5-9   |

| NR HDL Cell Search and MIB Recovery MATLAB Reference | 5-22  |

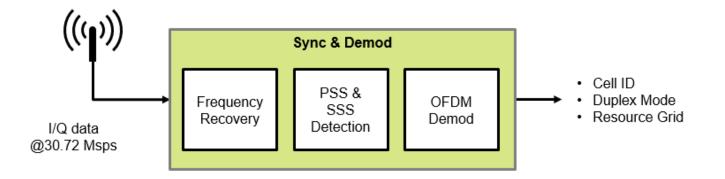

| NR HDL Cell Search                                   | 5-38  |

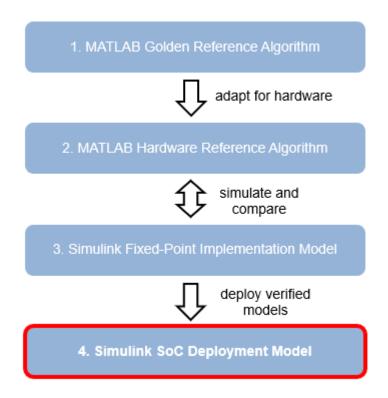

| Deploy NR HDL Reference Applications on SoCs         | 5-55  |

| LTE HDL Cell Search                                  | 5-57  |

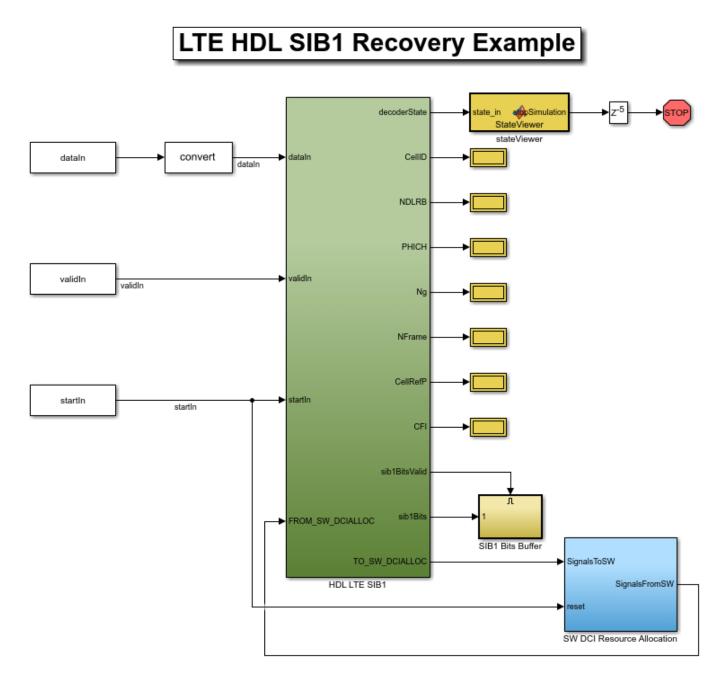

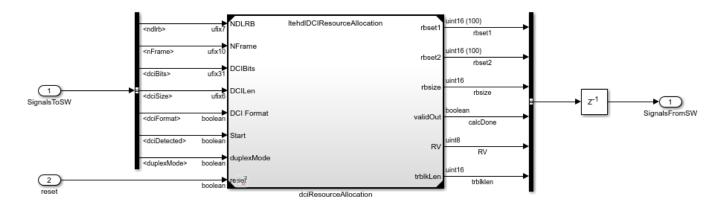

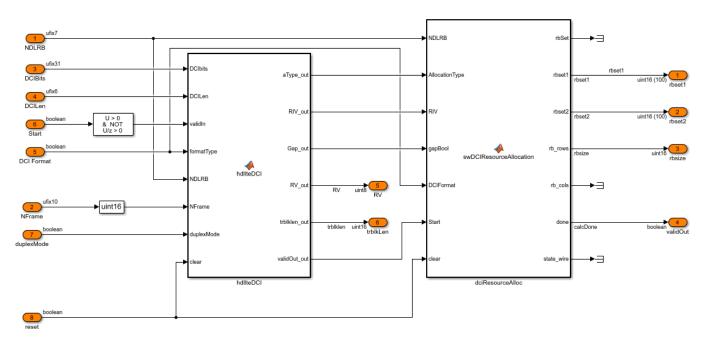

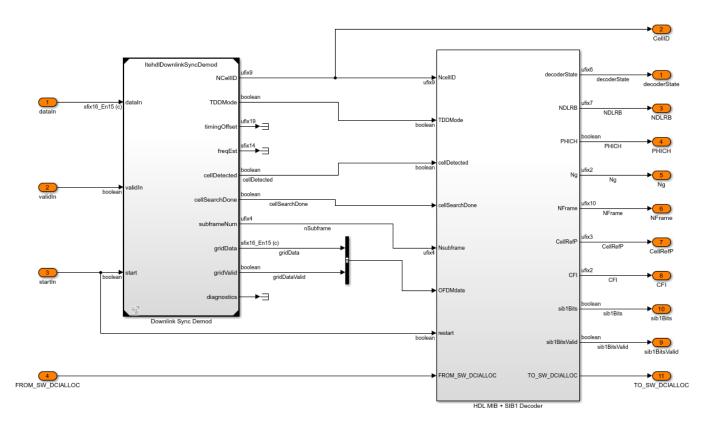

| LTE HDL SIB1 Recovery                                | 5-74  |

| LTE HDL MIB Recovery                                 | 5-92  |

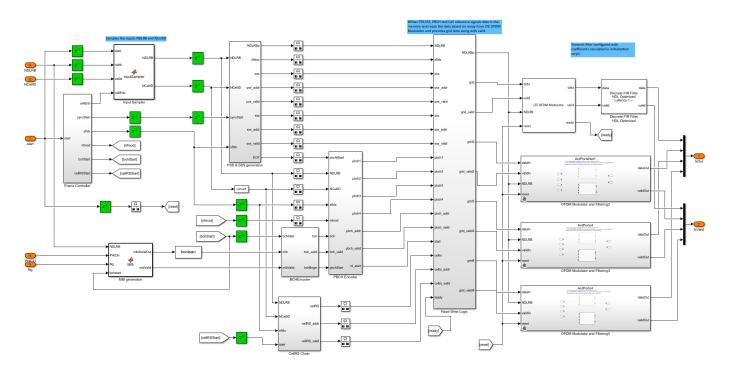

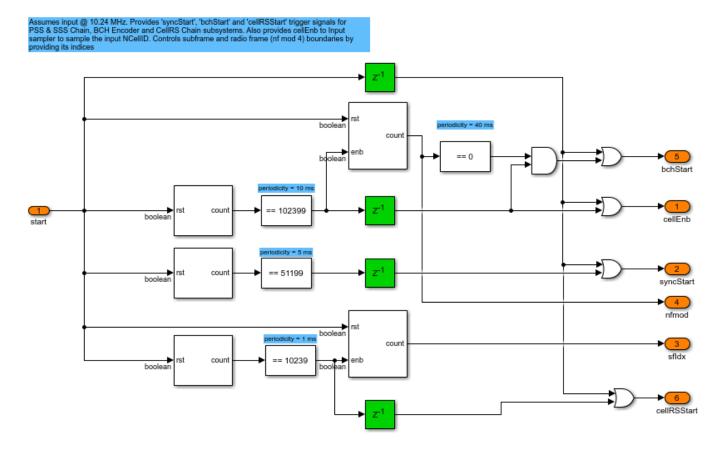

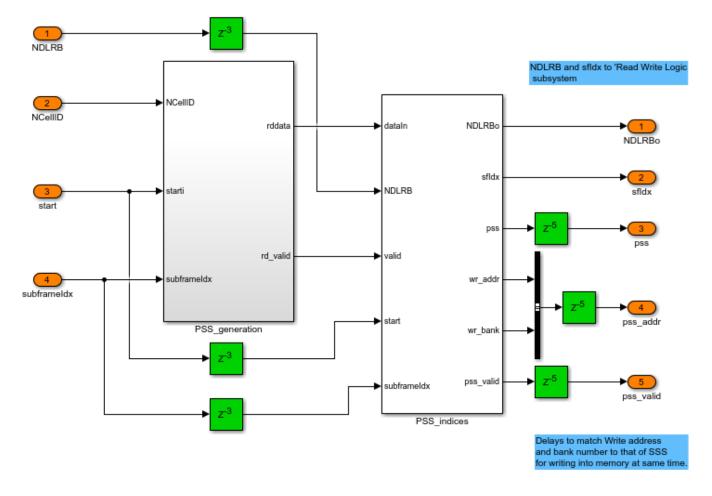

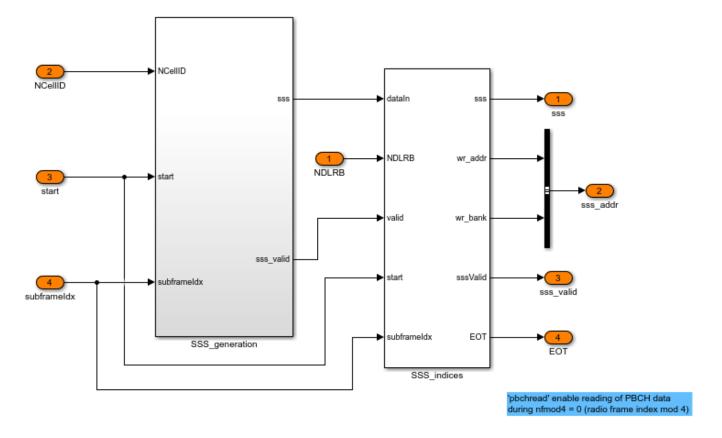

| LTE HDL PBCH Transmitter                             | 5-103 |

| Deploy LTE HDL Reference Applications on SoCs | 5-119 |

|-----------------------------------------------|-------|

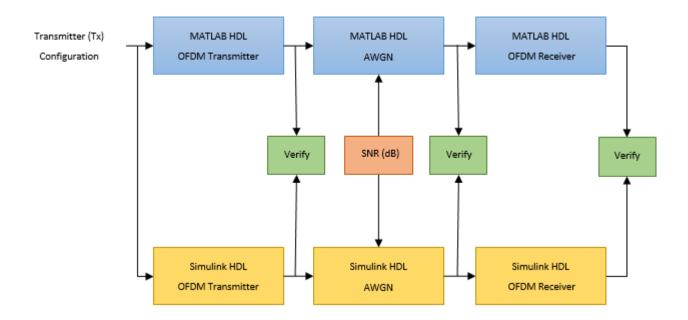

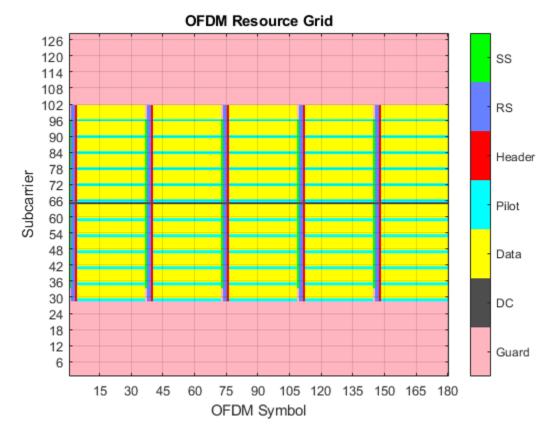

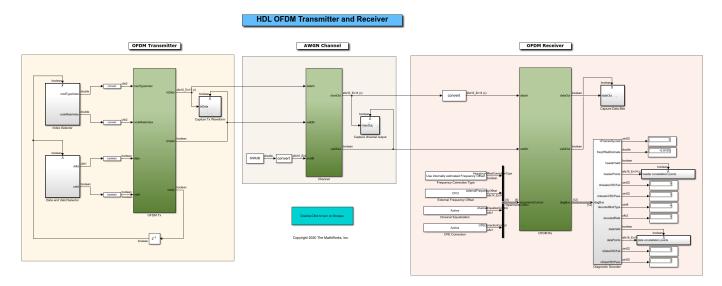

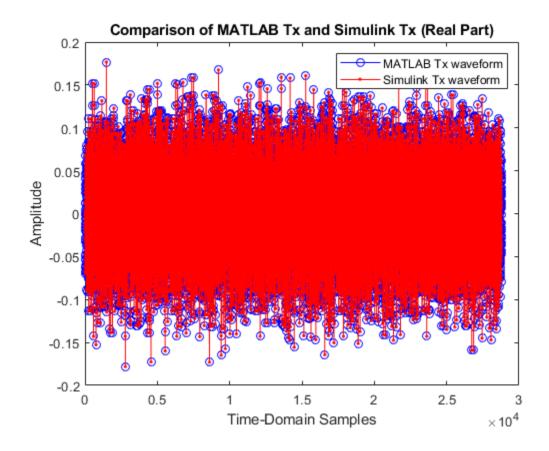

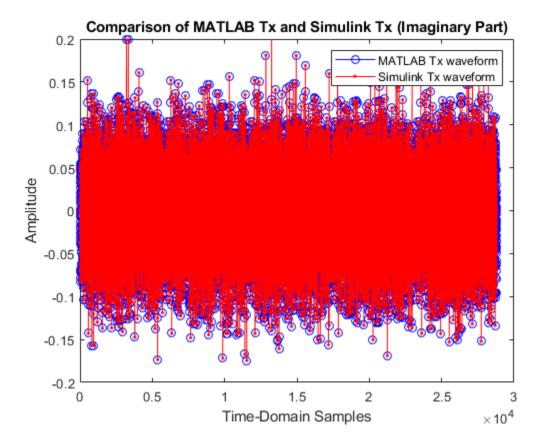

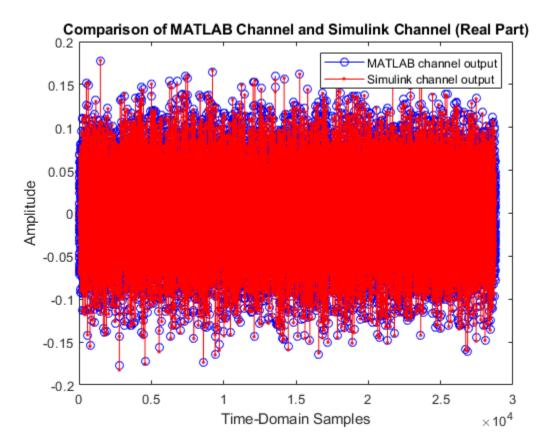

| HDL OFDM MATLAB References                    | 5-121 |

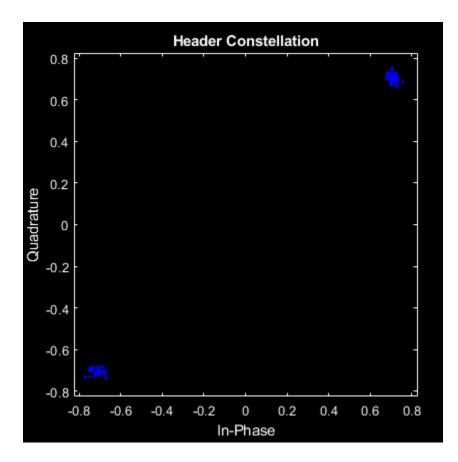

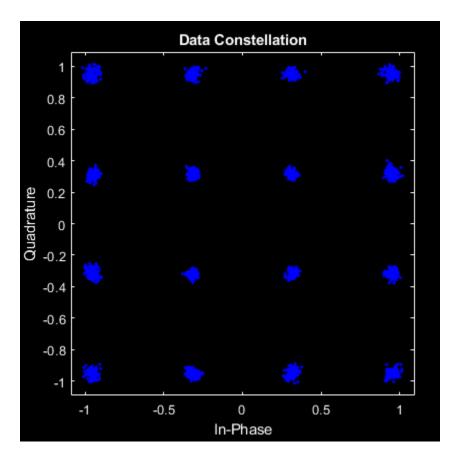

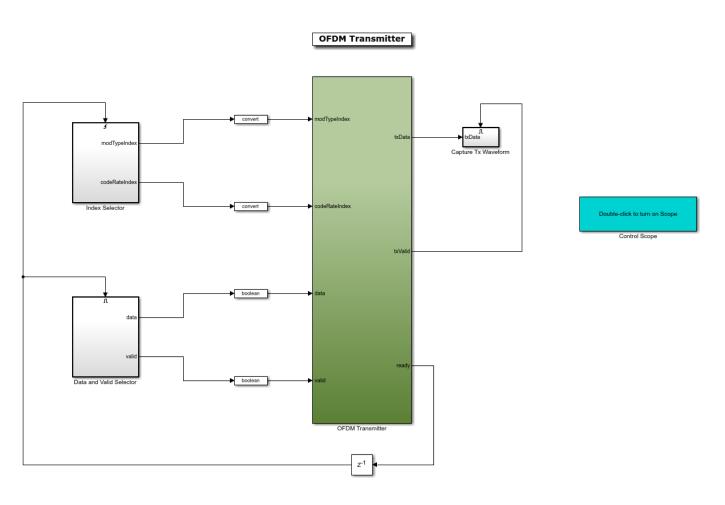

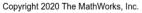

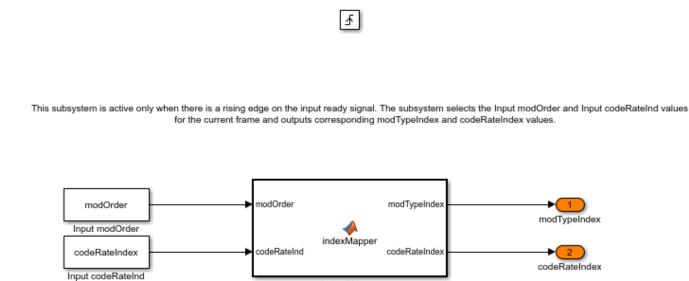

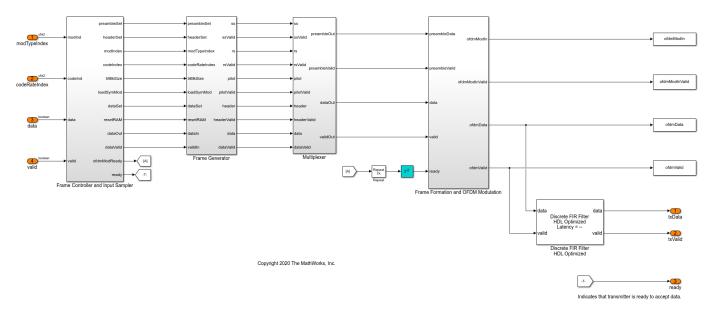

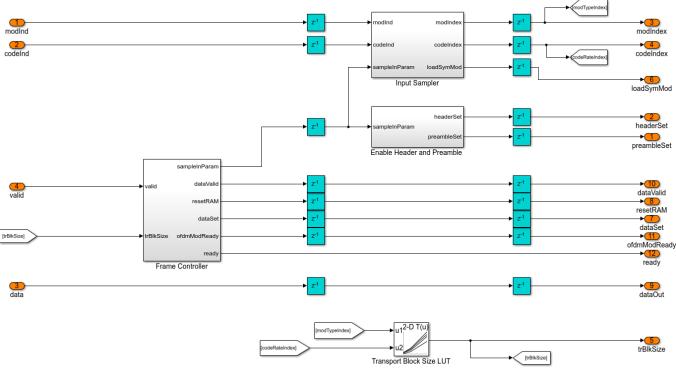

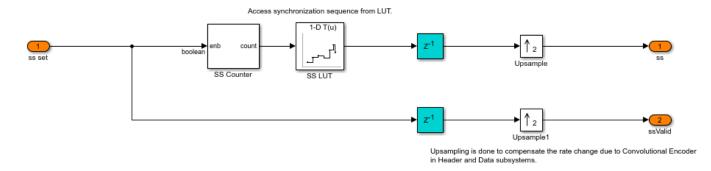

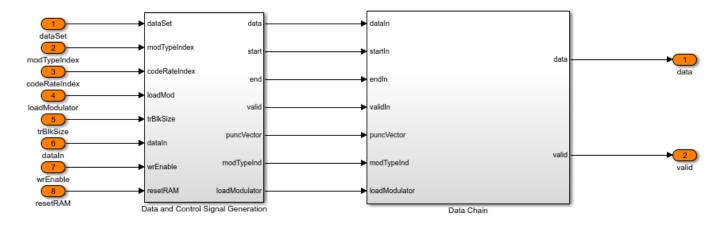

| HDL OFDM Transmitter                          | 5-135 |

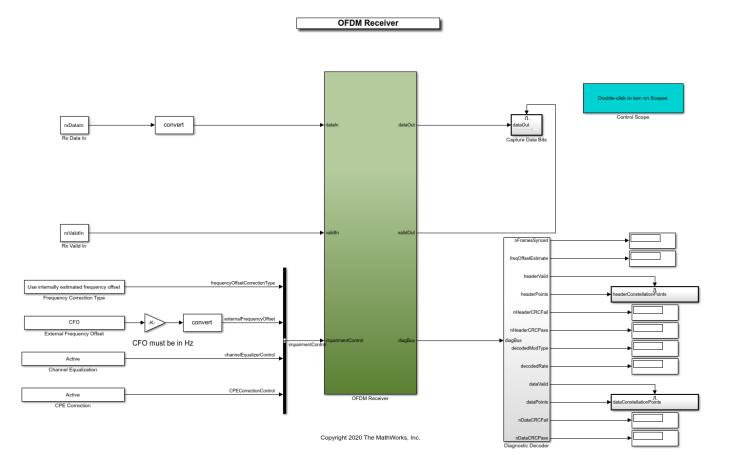

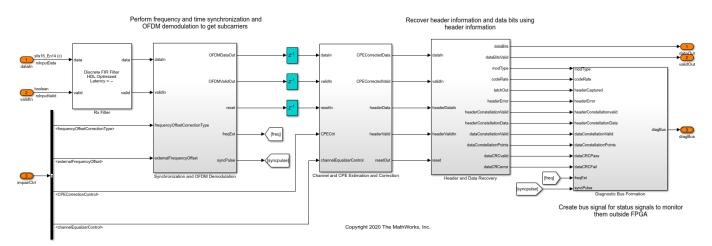

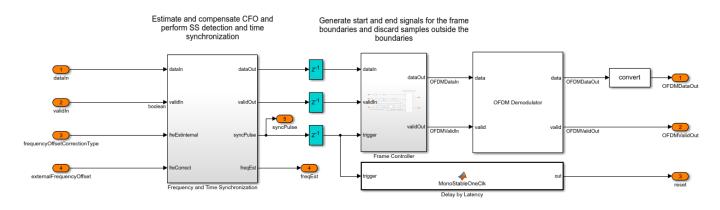

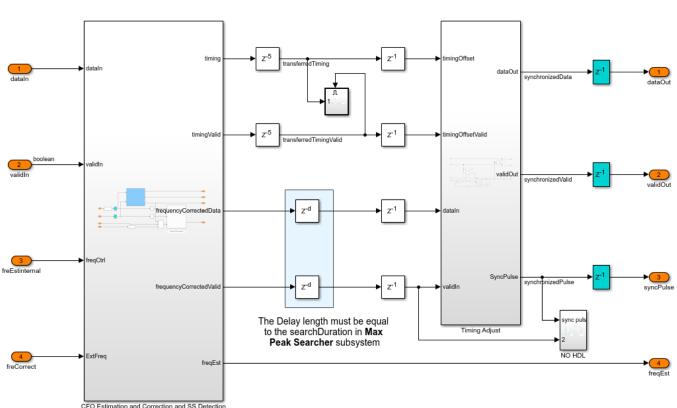

| HDL OFDM Receiver                             | 5-151 |

| Deploy Custom Communication Systems on SoCs   | 5-169 |

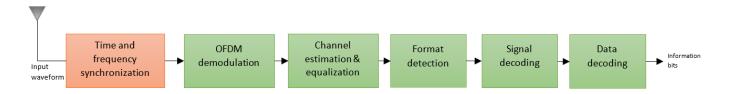

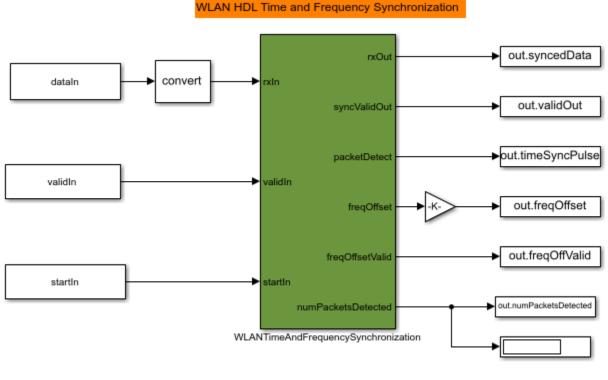

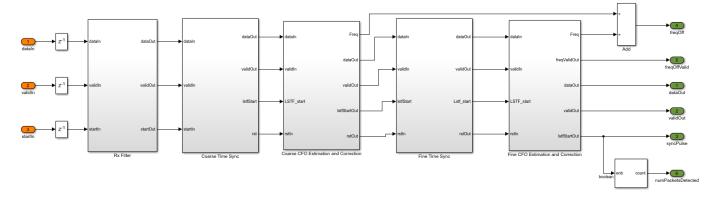

| WLAN HDL Time and Frequency Synchronization   | 5-171 |

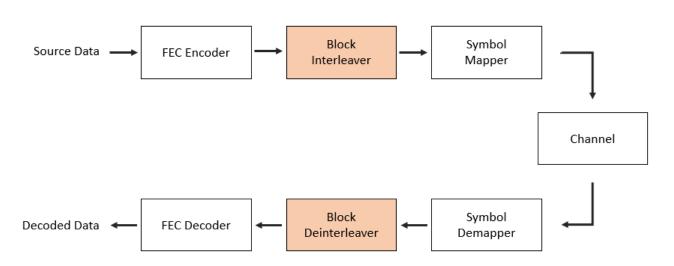

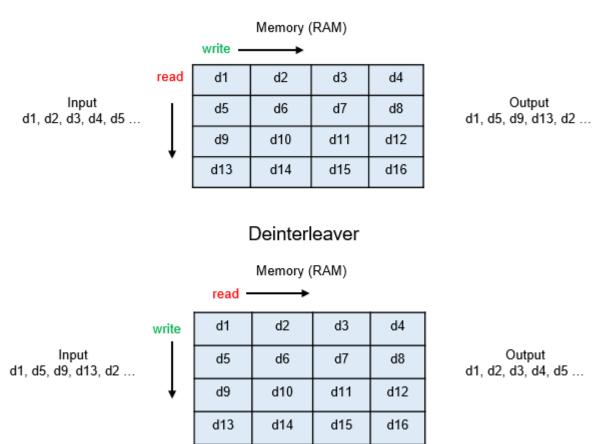

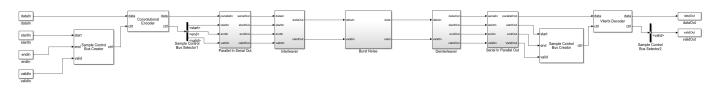

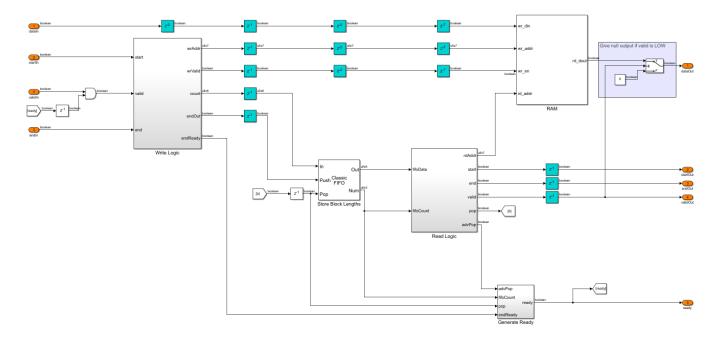

| HDL Interleaver and Deinterleaver             | 5-181 |

# **Model Architecture**

# **Streaming Sample Interface**

#### In this section...

"What Is a Streaming Sample Interface?" on page 1-2

"How Does a Streaming Sample Interface Work?" on page 1-2

"Why Use a Streaming Sample Interface?" on page 1-2

"Sample Stream Conversion" on page 1-3

"Timing Diagram of Serial Sample Interface" on page 1-3

"Using the nextFrame Output Signal" on page 1-4

# What Is a Streaming Sample Interface?

In hardware, processing an entire frame of data at one time has a high cost in memory and area. To save resources, serial processing is preferable in HDL designs. Wireless HDL Toolbox blocks operate on one sample at a time rather than a frame. The blocks accept and return data as a serial stream of samples and control signals. The control signals indicate the frame boundaries. The protocol mimics the characteristics of a real-world system, including inactive intervals between samples and frames.

# How Does a Streaming Sample Interface Work?

The control protocol uses start and end signals to demark each frame, and a valid signal to indicate which samples to process. The Wireless HDL Toolbox streaming sample protocol allows you to configure the number of idle cycles between samples and between frames. Idle cycles model the bursty character of real-world systems.

This protocol allows for frames of different sizes, such as if runt or partial frames enter the system due to synchronization changes.

# Why Use a Streaming Sample Interface?

#### Format Independence

The blocks that use this interface do not need a configuration option for an exact frame size or inactive intervals. In addition, if you change the input data timing for your design, you do not need to update each block. Instead, update the stream configuration once at the serialization step. Some blocks still require a maximum frame size parameter to allocate memory resources.

#### **Error Tolerance**

By using a streaming sample interface with control signals, each Wireless HDL Toolbox block starts computation on a fresh set of samples at the start-of-frame signal. Computations on the new frame occur whether or not the block receives the end signal for the previous frame.

The protocol tolerates minor timing errors. If the number of valid and invalid cycles between start and end signals varies, the blocks continue to operate correctly. This protocol makes the system resilient to runt frames and synchronization changes.

The Wireless HDL Toolbox encoder blocks require minimum between-frame spacing to accommodate insertion of codewords. The turbo and convolutional decoder blocks require that the previous frame

is decoded (has asserted the frame end signal) before the next frame arrives. The polar, LPDC, and RS encoder and decoder blocks provide a signal to indicate when the block is ready to receive the start of a new frame.

#### **Sample Stream Conversion**

Use the Frame To Samples block to convert framed data to a stream of samples and control signals that conform to this protocol. The control signals are grouped in a bus data type called samplecontrol.

The Frame To Samples block can serialize fixed-size frames. If your frames vary in size, use the whdlFramesToSamples function to convert framed data to vectors of samples and control signals in MATLAB<sup>®</sup>. Then import the vectors to Simulink<sup>®</sup>. Use the Sample Control Bus Creator block to create a samplecontrol bus in your model.

If your data is already in a serial format, design your own logic to generate these control signals from your existing serial control scheme.

#### **Supported Sample Data Types**

Wireless HDL Toolbox blocks have an input and output port, sample, for the streaming sample data. The blocks capture one sample at a time from the input, and produce one sample at a time for output. The samples can be one of these supported data types.

| Port   | Description                                                                                                                                                                          | Data Type                                                                                                                                                                                              |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sample | Scalar integer value that represents one sample.<br>The protocol also allows for a vector of integer<br>values that represent a single sample, such as for<br>turbo-encoded samples. | <ul> <li>Supported data types include:</li> <li>Boolean</li> <li>uint or int</li> <li>ufix or sfix</li> <li>double and single are supported for simulation but not for HDL code generation.</li> </ul> |

#### **Streaming Sample Control Signals**

Wireless HDL Toolbox blocks have an input and output port, ctrl, for the frame control signals relating to each sample. These three control signals indicate the validity of a sample and the boundaries of the frame. The control signal port is a nonvirtual bus data type called samplecontrol. For details of the bus data type, see "Sample Control Bus" on page 1-7.

## Timing Diagram of Serial Sample Interface

The timing diagram illustrates the streaming sample protocol. It shows a six-sample input frame and the equivalent sequence of control and data signals.

| ► frame    | 123456 | 12345 | 6 |   |   |     |   |    |   |   |   |    | 78 | 9 10 11 | 12 |

|------------|--------|-------|---|---|---|-----|---|----|---|---|---|----|----|---------|----|

| sample     |        | (1)(0 | 2 | 0 | 3 | ) O | 4 | χo | 5 | 0 | 8 | χo | 7  | χo      | (8 |

| ▼ ctrl     | 000    |       | X | χ | X | X   | X | X  | χ | X | X | X  | X  | X       | X  |

| — start    |        |       |   |   |   |     |   |    |   |   |   |    |    |         |    |

| - end      |        |       |   |   |   |     |   |    |   |   |   |    |    |         |    |

| ulid valid |        |       |   |   |   |     |   |    |   |   |   |    |    |         |    |

|            |        |       |   |   |   |     |   |    |   |   |   |    |    |         |    |

The input frame is ([1 2 3 4 5 6])', and the serializer is configured to insert idle cycles around the valid samples:

- One idle cycle between samples

- Three idle cycles between frames

- One value representing each sample (default output size)

You can specify these parameters by using either the Frame To Samples block or the whdlFramesToSamples function.

The control signals start and end are 1 for the first and last valid samples of the frame, respectively. The valid signal is 1 for each valid input sample. The valid signal is 0 for the idle cycles inserted between the samples and between the frames. The six-sample frame is now represented by streaming data over 15 cycles.

## Using the nextFrame Output Signal

The NR Polar Encoder, NR Polar Decoder, NR LDPC Encoder, NR LDPC Decoder, and RS Decoder blocks each provide an output signal to indicate when the block is ready to receive the start of a new frame. This signal is necessary because these blocks cannot accept a new frame at certain stages of internal computations, and the latency of those stages can vary with the values of input ports.

| Port | Description                                                                      | Data Type |

|------|----------------------------------------------------------------------------------|-----------|

|      | Boolean scalar that indicates when the block can accept the start of a new frame | Boolean   |

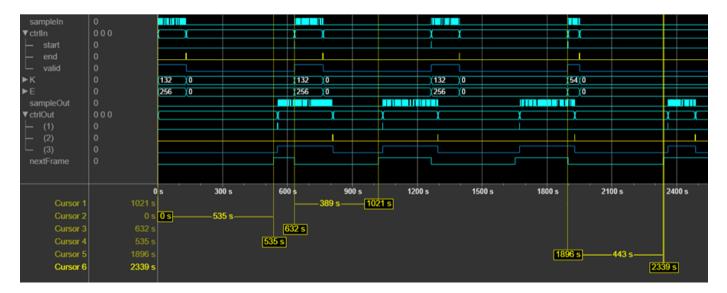

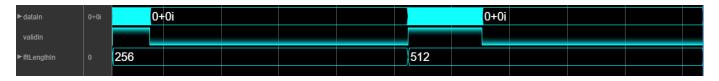

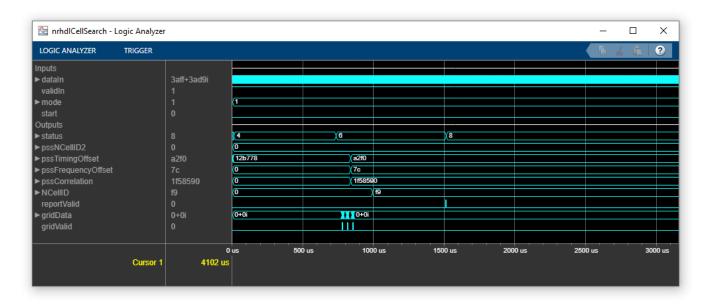

This waveform shows the NR Polar Encoder block processing several frames. The **nextFrame** output signal is 0 when the block is processing data, and 1 when the block is ready to receive the start of a new frame. The cursors show the latency varying with the values of the input **K** and **E** port values. For the first frame with given **K** and **E** values, the block must determine the message length and information bit mapping for those values. This configuration stage means the block needs some time before it is ready to accept the next input frame. For subsequent frames with the same values for **K** and **E**, the block is ready sooner because it does not need to recompute the configuration.

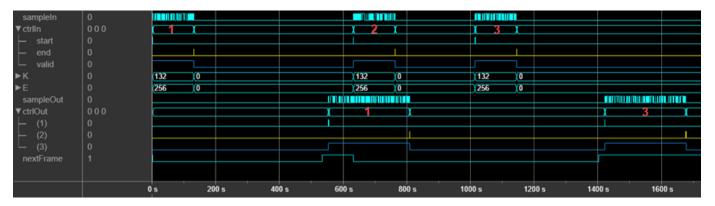

If the block receives an input **start** signal while **nextFrame** is 0, the block discards the frame in progress and begins processing the new data. This waveform shows an NR Polar Encoder input frame (3) applied when **nextFrame** is 0. The block discards the frame in progress (2) and processes the new frame (3) as normal.

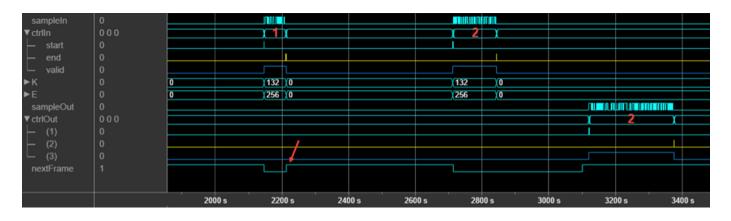

If the block receives an invalid input frame, for example, if the frame size is not within the supported range, then the block sets **nextFrame** to 1 one cycle after the input **end** signal. This behavior indicates that the input frame is discarded. This waveform shows an NR Polar Encoder input frame (1) that does not have the correct number of samples expected for the accompanying **K** and **E** values. The waveform shows the **nextFrame** signal set to 1 immediately after the input **end** signal from frame 1. The block discards the frame in progress (1) and processes the new frame (2) as normal.

## See Also

**Blocks** Frame To Samples | Samples To Frame

#### Functions

whdlFramesToSamples | whdlSamplesToFrames

#### **Related Examples**

- "Verify Turbo Decoder with Streaming Data from MATLAB"

- "Verify Turbo Decoder with Framed Data from MATLAB"

# **Sample Control Bus**

Wireless HDL Toolbox blocks use a nonvirtual bus data type, samplecontrol, for control signals associated with serial data. The bus contains three boolean signals indicating the validity of a sample and the boundaries of the frame. You can easily connect one block to another, because all Wireless HDL Toolbox blocks use this bus for input and output. To convert frames into a sample stream and a samplecontrol bus, use the Frame To Samples block. This block serializes fixed-size frames. If your frames vary in size, use the whdlFramesToSamples function to convert the frames to a data vector in MATLAB, and then import the data into Simulink.

| Signal | Description                            | Data Type |

|--------|----------------------------------------|-----------|

| start  | true for the first sample in the frame | Boolean   |

| end    | true for the last sample in the frame  | Boolean   |

| valid  | true for any valid sample              | Boolean   |

#### **Troubleshooting:**

When you generate HDL code from a Simulink model that uses this bus, you may need to declare an instance of samplecontrol bus in the base workspace. If you encounter the error Cannot resolve variable 'samplecontrol' when you generate HDL code in Simulink, use the samplecontrolbus function to create an instance of the bus type. Then try generating HDL code again.

To avoid this issue, the Wireless HDL Toolbox model template includes this line in the InitFcn callback.

```

evalin('base','samplecontrolbus')

```

You can also call this command from the MATLAB command line.

#### See Also

**Blocks** Frame To Samples | Samples To Frame

#### **More About**

• "Streaming Sample Interface" on page 1-2

# **Configure the Simulink Environment for Hardware Design**

#### **About Simulink Model Templates**

Simulink model templates provide common configuration settings and best practices for new models. Instead of using the default canvas of a new model, select a template model to help you get started.

For more information on Simulink model templates, see "Build and Edit a Model Interactively".

#### **Create Model Using Wireless HDL Toolbox Model Template**

- 1 Click the Simulink button, 🛅, or type simulink at the MATLAB command prompt.

- 2 On the Simulink start page, find the Wireless HDL Toolbox section, and click the **Streaming Data from MATLAB** or **Framed Data from MATLAB** template.

| New                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |       |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|---|

| Wireless                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | × | All 🗸 | Q |

| ✓ Wireless HDL Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |       |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |       |   |

| <ul> <li>- Statistical Control (Control (Contro) (Control (Control (Contro) (Contro) (Contro) (Contro) (Con</li></ul> | Construction of the second secon |   | _     |   |

A new model, with the template contents and settings, opens in the Simulink Editor. Select **Save** to save the model.

Alternatively, you can create a new model from the template on the command line. For example:

```

new_system my_whdl_Fmodel FromTemplate whdl_framed_data.sltx

open_system my_whdl_Fmodel

```

Or:

new\_system my\_whdl\_Smodel FromTemplate whdl\_streaming\_data.sltx

open\_system my\_whdl\_Smodel

#### Wireless HDL Toolbox Model Templates

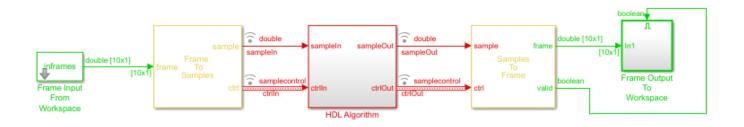

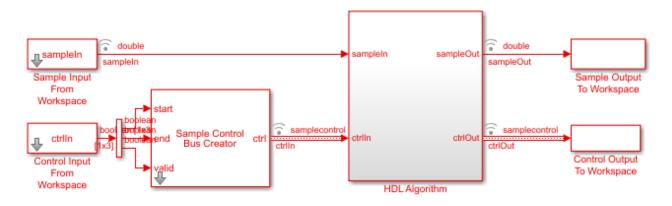

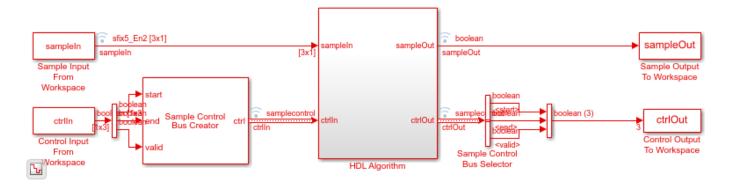

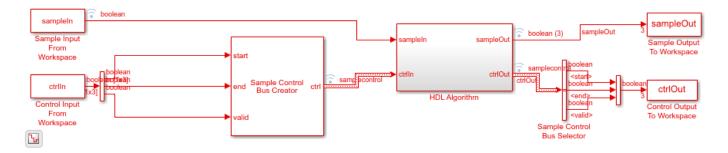

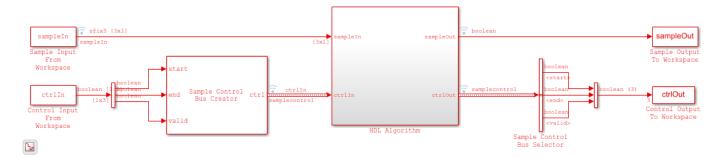

Both Wireless HDL Toolbox model templates include an empty subsystem, HDL Algorithm. This subsystem accepts and returns streaming data and accompanying control signals using the samplecontrolbus. You can design an HDL-targeted algorithm within this subsystem.

The templates also configure the model for HDL code generation. Both templates:

- Configure solver settings equivalent to calling hdlsetup

- Display data rates and data types in the Model Editor

- Create an instance of samplecontrolbus in the workspace (in InitFcn)

The simulation time, input data, and block parameters are defined in the callback function, InitFcn. To view or edit this function, on the **Modeling** tab, expand **Model Settings** and click **Model Properties**, and then on the **Callbacks** tab, click InitFcn\*.

#### **Framed Data Template**

The **Framed Data from MATLAB** template imports framed data from the MATLAB workspace, assuming all frames are the same size. Then, it converts the data to a sample stream by using the Frame To Samples block.

The output of the HDL Algorithm subsystem is connected to a Samples To Frame block. This block converts the output back to framed data for export to the MATLAB workspace.

The InitFcn defines placeholder input frames and settings for the Frame Input From Workspace, Frame To Samples, and Samples To Frame blocks.

The StopFcn applies the valid signal to the output data and creates a single variable in the workspace.

The model has one data rate for the framed data and a faster data rate for the sample stream. You can display these rates as different colors in the Simulink model.

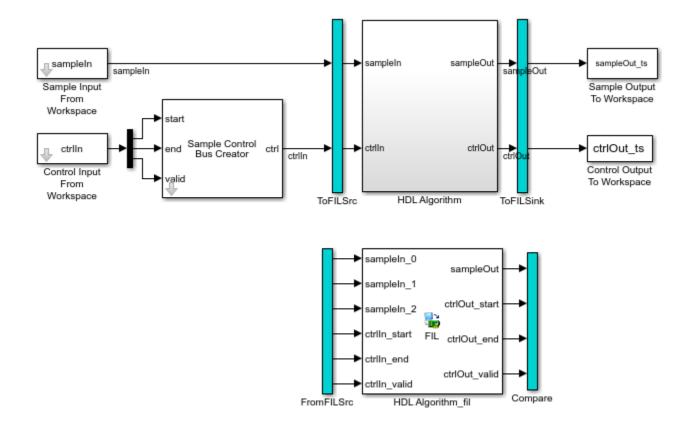

#### **Streaming Data Template**

Use the **Streaming Data from MATLAB** template when your data stream has different-sized frames. The InitFcn defines placeholder input frames and uses the whdlFramesToSamples function to convert framed data to vectors of data and control signals. The From Workspace block imports these variables to the model.

To connect to the HDL Algorithm subsystem and any Wireless HDL Toolbox blocks that you add inside it, the model converts the control signals to the samplecontrolbus type, using the Sample Control Bus Creator block.

The model exports the streaming data and control signals back to the MATLAB workspace. The StopFcn uses the whdlSamplesToFrames function to convert them back to framed data.

The model has a single data rate because all signals in the model represent streaming samples.

# See Also

#### Blocks

Frame To Samples | Sample Control Bus Creator | Samples To Frame

#### Functions

whdlFramesToSamples | whdlSamplesToFrames

#### **More About**

• "Streaming Sample Interface" on page 1-2

# **HDL Code Generation Support**

You can use Simulink for rapid prototyping of hardware designs. Wireless HDL Toolbox blocks, when used with HDL Coder<sup>m</sup>, support HDL code generation. HDL Coder tools generate target-independent synthesizable Verilog<sup>®</sup> and VHDL<sup>®</sup> code for FPGA programming or ASIC prototyping and design.

#### HDL Code Generation Support in Wireless HDL Toolbox

Most blocks in Wireless HDL Toolbox support HDL code generation.

The following blocks are for simulation only and are not supported for HDL code generation:

- Frame To Samples

- Samples To Frame

- FIL Frame To Samples

- FIL Samples To Frame

## **Other Blocks Supporting HDL Code Generation**

Other MathWorks<sup>®</sup> products also include blocks supported for HDL code generation that you can use to build up your design.

In the Simulink library browser, you can find libraries of blocks supported for HDL code generation in the **HDL Coder**, **Communications Toolbox HDL Support**, **DSP System Toolbox HDL Support** block libraries, and others.

To create a library of HDL-supported blocks from all your installed products, enter hdllib at the MATLAB command line. This command requires an HDL Coder license.

You can also view blocks that are supported for HDL code generation in documentation by filtering the block reference list. Click **Blocks** in the blue bar at the top of the Help window, then select the **HDL code generation** check box at the bottom of the left column. The blocks are listed in their respective products. You can use the table of contents in the left column to navigate between products and categories.

Refer to the "Extended Capabilities > HDL Code Generation" section of each block page for block implementations, properties, and restrictions for HDL code generation.

| Documentation                                    | All Exa                   | Imples Functions    | Blocks Apps        | Search Help Q                                                                         |  |

|--------------------------------------------------|---------------------------|---------------------|--------------------|---------------------------------------------------------------------------------------|--|

| ■ CONTENTS                                       | Close                     |                     |                    |                                                                                       |  |

| « Documentation Home                             |                           | DSP System T        | oolbox — Bloc      | ks                                                                                    |  |

| « Blocks                                         |                           |                     |                    |                                                                                       |  |

| Category                                         |                           |                     |                    | By Category Alphabetical List                                                         |  |

| DSP System Toolbox                               |                           | Results are filtere | ed                 |                                                                                       |  |

| Signal Generation,<br>Manipulation, and Analysis | 21                        |                     |                    |                                                                                       |  |

| Filter Implementation                            | 10                        | Signal Generation   | n, Manipulation, a | nd Analysis                                                                           |  |

| Transforms and Spectral<br>Analysis              | 3                         | Signal Operations   |                    |                                                                                       |  |

| Statistics and Linear Algebra                    | 3                         | Downsample          | Resample           | input at lower rate by deleting samples                                               |  |

| Fixed-Point Design                               | 8                         | Repeat              | Resample           | input at higher rate by repeating values                                              |  |

| HDL Coder                                        |                           | Sample and Hold     | Sample an          | d hold input signal                                                                   |  |

| HDL Verifier                                     |                           | Upsample            | Resample           | input at higher rate by inserting zeros                                               |  |

| LTE HDL Toolbox                                  |                           | DC Blocker          | Block DC           | component                                                                             |  |

| Mixed-Signal Blockset                            |                           | Signal Generation   |                    |                                                                                       |  |

| SerDes Toolbox                                   |                           | Constant            | Generate           | constant value                                                                        |  |

| SimEvents                                        |                           | NCO                 | Generate           | eal or complex sinusoidal signals                                                     |  |

| Simulink Test                                    | -                         | NCO HDL Optimized   |                    | eal or complex sinusoidal signals—optimized for HDL code generation                   |  |

|                                                  |                           | Sine Wave           | Generate           | continuous or discrete sine wave                                                      |  |

| Extended Capability                              |                           |                     |                    |                                                                                       |  |

| C/C++ Code Generation                            | 34                        | Scopes and Data Lo  | ogging             |                                                                                       |  |

| HDL Code Generation                              | 36                        | Spectrum Analyzer   | Display fre        | Display frequency spectrum                                                            |  |

| PLC Code Generation                              | 4                         | Time Scope          | Display an         | Display and analyze signals generated during simulation and log signal data to MATLAB |  |

| Fixed-Point Conversion                           | Fixed-Point Conversion 28 |                     | Display ma         | trices as color images                                                                |  |

|                                                  |                           | Waterfall           | View vecto         | rs of data over time                                                                  |  |

|                                                  |                           | To Workspace        | Write data         | to MATLAB workspace                                                                   |  |

## **Streaming Sample Interface in HDL**

The streaming sample control bus data type used by Wireless HDL Toolbox blocks is flattened into separate signals in HDL.

In VHDL, the interface is declared as:

```

PORT( clk

std_logic;

:

IΝ

reset

:

IN

std logic;

enb

:

IN

std_logic;

in0

:

ΙN

std_logic_vector(7 DOWNTO 0); -- uint8

in1_start

:

IN

std_logic;

in1_end

std_logic;

:

IN

in1_valid

:

IN

std_logic;

out0

0UT

std_logic_vector(7 DOWNTO 0); -- uint8

:

std_logic;

out1_start

0UT

:

std_logic;

std_logic

out1 end

:

0UT

out1_valid

0UT

:

);

```

In Verilog, the interface is declared as:

```

input clk;

input reset;

input enb;

input [7:0] in0; // uint8

input in1_start;

input in1_end;

input in1_valid;

output [7:0] out0; // uint8

output out1_start;

output out1_end;

output out1_valid;

```

# See Also

#### **More About**

- "Streaming Sample Interface" on page 1-2

- "Generate HDL Code" on page 2-5

# Generate HDL Code

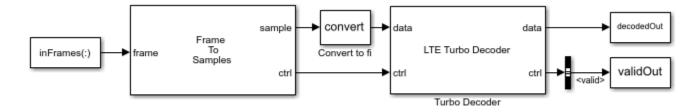

You can generate HDL code from subsystems that include blocks supported for HDL code generation, such as the model in "Verify Turbo Decoder with Streaming Data from MATLAB". In that example, you can generate HDL code from the HDL Algorithm subsystem.

To generate HDL code, you must have an HDL Coder license.

#### **Prepare Model**

Run hdlsetup to configure the model for HDL code generation. If you started your design using the Wireless HDL Toolbox Simulink model template, your model is already configured for HDL code generation.

#### **Generate HDL Code**

Right-click the HDL Algorithm subsystem, and select **HDL Code > Generate HDL for Subsystem** to generate HDL using the default settings. The output log of this operation is shown in the MATLAB Command Window, along with the location of the generated files.

To change code generation options, use the **HDL Code Generation** panes of the Simulink Configuration Parameters dialog box. For guidance through the HDL code generation process, or to select a target device or synthesis tool, right-click the HDL Algorithm subsystem, and select **HDL Code > HDL Workflow Advisor**.

Alternatively, from the MATLAB Command Window, you can call:

```

makehdl([modelname '/HDL Algorithm'])

```

#### **Generate HDL Test Bench**

You can select options to generate a test bench in the Simulink Configuration Parameters dialog box or in the HDL Workflow Advisor.

Alternatively, to generate an HDL test bench from the command line, call:

```

makehdltb([modelname '/HDL Algorithm'])

```

#### See Also

Functions

makehdl|makehdltb

#### **Related Examples**

- "HDL Code Generation and FPGA Synthesis from Simulink Model" (HDL Coder)

- "Choose a Test Bench for Generated HDL Code" (HDL Coder)

# **FPGA-in-the-Loop**

FPGA-in-the-loop (FIL) enables you to run a Simulink simulation that is synchronized with an HDL design running on an Intel<sup>®</sup> or Xilinx<sup>®</sup> FPGA board. This link between the simulator and the board enables you to verify HDL implementations directly against Simulink or MATLAB algorithms. You can apply real-world data and test scenarios from these algorithms to the HDL design on the FPGA.

When simulating Wireless HDL Toolbox blocks, you must use a streaming sample interface. Streaming sample data, while required for hardware implementations of communications systems, is time-consuming at the FPGA-in-the-loop interface with Simulink.

You can convert from frames to samples and samples to frames either in Simulink or in MATLAB. Depending on your workflow, you can optimize your FPGA-in-the-loop simulation in one of two ways.

One workflow is a Simulink model that imports framed data from MATLAB. This type of model then uses the Frame To Samples and Samples To Frame blocks to convert the data format. For FPGA-in-the-loop, replace these conversion blocks with FIL Frame To Samples and FIL Samples To Frame blocks.

The other workflow is a Simulink model that imports streaming data from MATLAB. This type of model goes with a MATLAB script that uses the ltehdlFrameToSamples and ltehdlSamplesToFrames functions. For FPGA-in-the-loop, modify your script and Simulink model so that they pass vectors of data to the FPGA-in-the-loop interface.

When you generate a programming file for a FIL target in Simulink, the tool creates a model to compare the FIL simulation with your Simulink design. For Wireless HDL Toolbox designs, the FIL block in that model replicates the sample-streaming interface and sends one sample at a time to the FPGA. Both these modifications construct vectors that make more efficient use of the interface between the Simulink model and the FPGA board.

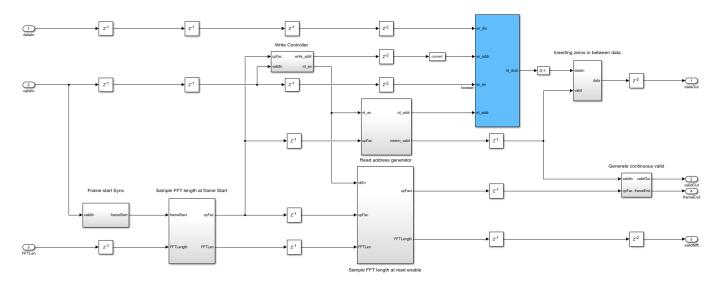

The instructions that follow show how to modify FPGA-in-the-loop models for the "Verify Turbo Decoder with Streaming Data from MATLAB" and "Verify Turbo Decoder with Framed Data from MATLAB" workflow examples.

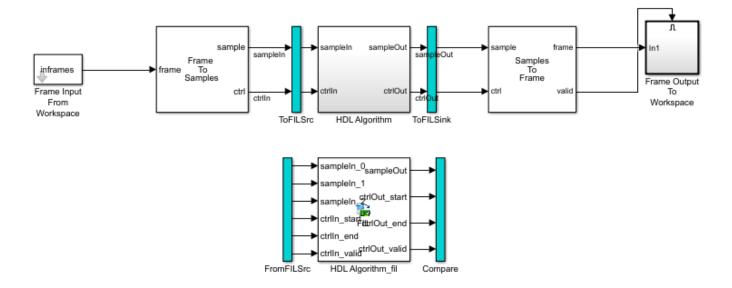

## FIL Workflow: Framed Data from MATLAB

#### Autogenerated FIL Model

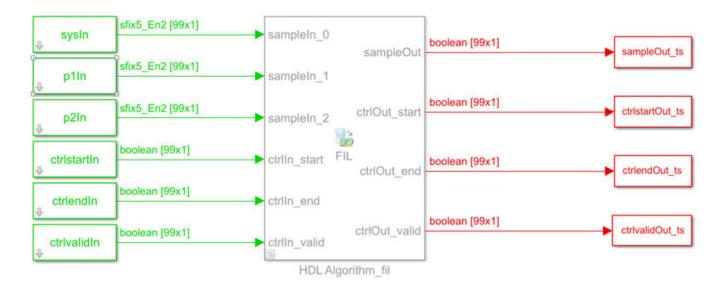

The generated model, including the FIL block that interfaces with the FPGA board, is shown for a model that converts to streaming samples in Simulink. If each sample is represented by multiple values, then the values are flattened into separate ports for FIL.

The blue ToFILSrc subsystem branches the sample-stream input of the HDL Algorithm block to the FromFILSrc subsystem. The blue ToFILSink subsystem branches the sample-stream output of the HDL Algorithm block into the Compare subsystem, where it is compared with the output of the HDL Algorithm\_fil block. This setup is slow because the model sends only a single sample, and its associated control signals, in each packet to and from the FPGA board.

#### **Modified FIL Model**

To improve the communication bandwidth with the FPGA board, modify the autogenerated model. The modified model uses the FIL Frame To Samples and FIL Samples To Frame blocks to send one frame at a time.

To create this modified FIL model:

**1** Remove the blue subsystems, and create a branch at the **frame** input port of the Frame To Samples block.

- 2 Insert the FIL Frame To Samples block before the HDL Algorithm\_fil block. Insert the FIL Samples To Frame block after the HDL Algorithm fil block.

- **3** Set the **Output frame size** on the FIL block to the input frame size.

| Runtime Options      |               |  |

|----------------------|---------------|--|

| Overclocking factor: | 1 ~           |  |

| Output frame size:   | inframesize ~ |  |

- 4 In the FIL Frame To Samples and FIL Samples To Frame blocks, set the parameters to match the settings of the Frame To Samples and Samples To Frame blocks.

- **5** Branch the frame output of the Samples To Frame block for comparison. You can compare the entire frame at once with a Diff block. Compare the validOut signals using an XOR block.

The input size at the FIL block is the frame size from the input data frames. The vector size of the FIL block ports does not modify the generated HDL code. It affects only the packet size of the communication between the simulator and the FPGA board. This modified model sends an entire frame to the FPGA board in each packet, significantly improving the efficiency of the communication link.

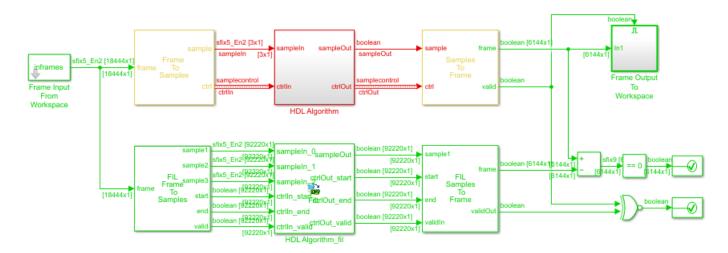

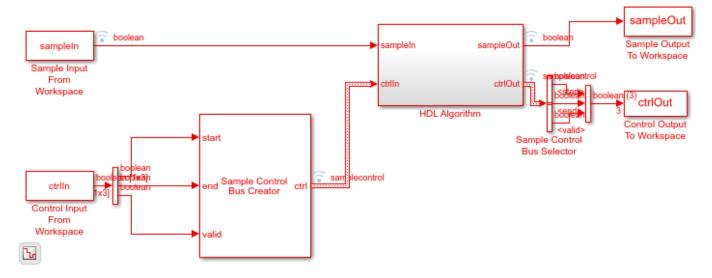

## FIL Workflow: Streaming Data from MATLAB

#### Autogenerated FIL Model

The generated model, including the FIL block that interfaces with the FPGA board, is shown for a model that converts to streaming samples in MATLAB. If each sample is represented by multiple values, then the values are flattened into separate ports for FIL.

The blue ToFILSrc subsystem branches the sample-stream input of the HDL Algorithm block to the FromFILSrc subsystem. The blue ToFILSink subsystem branches the sample-stream output of the HDL Algorithm block into the Compare subsystem, where it is compared with the output of the HDL Algorithm\_fil block. This setup is slow because the model sends only a single sample, and its associated control signals, in each packet to and from the FPGA board.

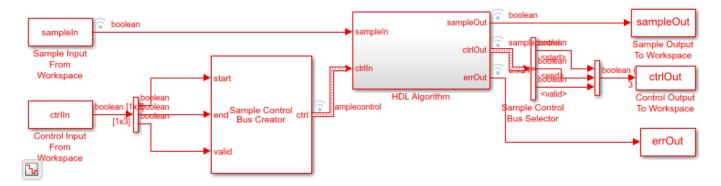

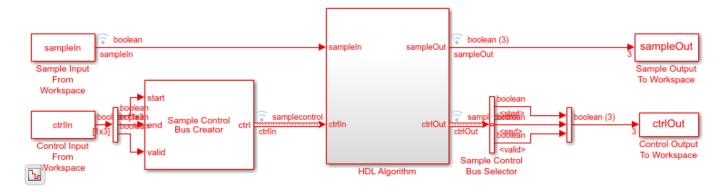

#### **Modified FIL Model**

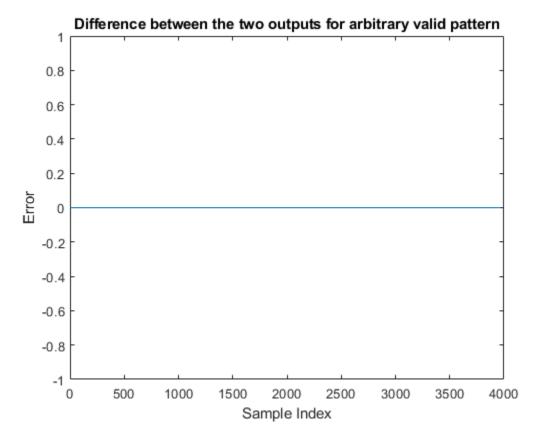

To improve the communication bandwidth with the FPGA board, use the generated FIL block in a different model. The alternate model imports and exports vectors of flattened data. The accompanying MATLAB script reshapes the input and output data, and verifies the FIL output against a behavioral model. Reshaping the data in MATLAB is easier and the simulation is faster than reshaping in Simulink.

First, modify the accompanying MATLAB script:

1 Pick a frame size for the FIL simulation. This size does not have to match the actual frame sizes in the generated data. It can contain your entire data set. The FIL block divides the data into maximum size packets for communication with the FPGA board.

filframesize = 99;

2 Combine the cell array of input frames into one matrix.

allframes = [inframes{:}];

**3** Flatten the samples and control signals so there is one vector for each input port on the FIL block. This model includes the LTE Turbo Decoder block, so the input samples consist of three values.

```

sysIn = allframes(1:3:end);

plIn = allframes(2:3:end);

p2In = allframes(3:3:end);

ctrlstartIn = ctrlIn(1:3:end);

ctrlendIn = ctrlIn(2:3:end);

ctrlvalidIn = ctrlIn(3:3:end);

```

4 Call the FIL model.

```

simTime = size(allframes,1);

modelname = 'TurboDecoderStreamingFILVectortoSL';

open_system(modelname);

sim(modelname);

```

5 Reshape the output variables for input to the whdlSamplesToFrames function. Recreate an *N*-by-3 control signal matrix and a vector of sample data. In this example, the output sample is a single value. If the output sample is multiple values, build an *N*-by-*SampleSize* sample matrix.

```

sampleOut = squeeze(sampleOut_ts.Data);

ctrlOut = [squeeze(ctrlstartOut_ts.Data) ...

```

squeeze(ctrlendOut\_ts.Data) ...

squeeze(ctrlvalidOut\_ts.Data)];

Then, create a Simulink model:

- **1** Copy the generated FIL block into a new model.

- **2** Configure and connect a Signal From Workspace block for each input port on the FIL block. Use the variables from your MATLAB script as the parameter values.

| Parameters              |   |

|-------------------------|---|

| Signal:                 |   |

| sysIn                   | : |

| Sample time:            |   |

| sampletime/filframesize | : |

| Samples per frame:      |   |

| filframesize            | : |

**3** Set the **Output frame size** on the FIL block to the desired FIL frame size.

| Runtime Options      |                |  |

|----------------------|----------------|--|

| Overclocking factor: | 1 ~            |  |

| Output frame size:   | filframesize ~ |  |

4 Configure and connect a To Workspace block for each output port of the FIL block.

The input size at the FIL block is the frame size you specify on the Signal To Workspace blocks. The vector size of the FIL block ports does not modify the generated HDL code. It affects only the packet size of the communication between the simulator and the FPGA board. This modified model sends an entire frame to the FPGA board in each packet, significantly improving the efficiency of the communication link.

#### See Also

#### **More About**

- "Verify Turbo Decoder with Streaming Data from MATLAB"

- "Verify Turbo Decoder with Framed Data from MATLAB"

# **Prototype Wireless Communications Algorithms on Hardware**

The Communications Toolbox<sup>™</sup> Support Package for Xilinx Zynq-Based Radio enables you to design, prototype, and verify practical wireless communications systems on Xilinx Zynq-based radio hardware.

- Use the Xilinx Zynq-based radio as an I/O peripheral to transmit and receive real-time arbitrary waveforms using MATLAB System objects or Simulink blocks.

- Transmit and receive RF signals out of the box, enabling quick testing of SDR designs under realworld conditions.

- Transmit and receive data on one or two channels.

- Configure RF radio settings easily.

- Acquire high-bandwidth signals by using burst mode.

- In Simulink, customize and prototype SDR algorithms. Target only the FPGA fabric of the device, or deploy partitioned hardware-software co-design implementations across the ARM<sup>®</sup> processor and the FPGA fabric of the device (Windows<sup>®</sup> operating system only).

- Run application examples to get started.

The support package provides two workflows:

- FPGA-only targeting This workflow uses generated HDL code from HDL Coder and HDL Coder Support Package for Xilinx Zynq Platform.

- Hardware-software co-design This workflow also uses HDL Coder and HDL Coder Support Package for Xilinx Zynq Platform. It additionally requires Simulink Coder<sup>™</sup>, Embedded Coder<sup>®</sup>, and Embedded Coder Support Package for Xilinx Zynq Platform.

The "LTE MIB Recovery and Cell Scanner Using Analog Devices AD9361/AD9364" (Communications Toolbox Support Package for Xilinx Zynq-Based Radio) support package example shows how to use the hardware-software co-design workflow to deploy the design from "LTE HDL MIB Recovery" on page 5-92 to a hardware board with a radio daughter card. The "LTE Receiver Using Analog Devices AD9361/AD9364" (Communications Toolbox Support Package for Xilinx Zynq-Based Radio) support package example shows how to capture live LTE data for use in testing your designs.

#### How to Install Support Packages

A support package is an add-on that enables you to use a MathWorks product with specific third-party hardware and software. Support packages use the license of the base product. For instance, Communications Toolbox Support Package for Xilinx Zynq-Based Radio requires a license for Communications Toolbox.

Install support packages using the MATLAB **Add-Ons** menu. You can also use the **Add-Ons** menu to update installed support package software or update the firmware on third-party hardware.

To install support packages, on the MATLAB **Home** tab, in the **Environment** section, click **Add-Ons** > **Get Hardware Support Packages**. You can filter this list by selecting categories (such as hardware vendor or application area), or by performing a keyword search.

Search the Add-Ons list for Zynq, and install these support packages:

Communications Toolbox Support Package for Xilinx Zynq-Based Radio

- HDL Coder Support Package for Xilinx Zynq Platform

- Embedded Coder Support Package for Xilinx Zynq Platform (only needed for hardware-software co-design)

When the support package installation is complete, you must set up the host computer and radio hardware. For Windows systems, the installer provides guided setup steps. For Linux<sup>®</sup> systems, the installer links to manual setup instructions.

### **Design Requirements**

The Communications Toolbox Support Package for Xilinx Zynq-Based Radio provides a reference design that you can use to create an IP core that integrates into the radio hardware. Use the HDL Workflow Advisor to guide you through generating a shareable and reusable IP core module using the reference design.

To work with the reference design, your FPGA targeted design must use a streaming data interface with a control signal that indicates the validity of each sample. Wireless HDL Toolbox blocks provide this interface. Use the Sample Control Bus Selector block to separate the valid control signal from the bus.

To deploy a design using the support package, your design must meet these preconditions.

- Each data input or output must be 16 bits. The HDL subsystem that fits into the reference design does not support complex signals at the ports. To handle complex inputs and outputs, model separate I and Q ports at the subsystem boundaries.

- Model all the ports for a given reference design, even when the ports are not used.

- In Simulink, the input and output data and valid signals must be driven at the same sample rate. Therefore, the input and output clock rates of the subsystem must be equal.

- Clock the data and valid signals at the fastest rate of the HDL subsystem.

- For the FPGA-only targeting workflow:

- Duplex operation is not supported. Use either the transmit or the receive operation, but not both.

- For the hardware-software co-design workflow:

- Duplex operation is supported. You can use both the Transmitter and Receiver blocks in the same design.

- AXI4-Lite register ports can be clocked at arbitrary rates.

- In single-channel mode, you can transmit or receive data frames containing an even number of samples only. If you use an odd number of samples, the software inserts a zero sample at the end of each frame.

The real-time design encounters a larger volume of data and a larger set of state progressions than you can simulate in Simulink. Make sure to model and generate control logic to handle the restart between subframes. Consider adding extra subsystem ports for debug visibility of these extended states once the design is deployed to the board.

## **Design for Debugging**

Once the design is deployed to the board, you have much less visibility of the internal signals in your design. To improve visibility, you can add temporary output ports to your subsystem before you

generate your IP core. Signals that can help with debugging are design state, mux select signals or other control parameters, and data values at intermediate stages of the data path. You can also add input ports and muxes to give the option for external control of parameters such as mux select signals and gain values.

When you simulate the design on the board in External mode, you can drive and view these ports from Simulink. The Xilinx Zynq AXI Interface block from the generated software model provides a Simulink interface to the input and output ports of your design while it is running on the board.

Once you are confident that your design is behaving as intended, you can remove these ports and regenerate the IP core.

Another debugging strategy is to include a known input signal stored in memory on the FPGA. This memory can be part of the generated HDL code from your Simulink model. The "LTE MIB Recovery and Cell Scanner Using Analog Devices AD9361/AD9364" (Communications Toolbox Support Package for Xilinx Zynq-Based Radio) support package example shows an input port externalDataSel that provides a switch between a stored data set and the live data from the radio.

# See Also

#### **More About**

- "Communications Toolbox Support Package for Xilinx Zynq-Based Radio"

- "FPGA Targeting Workflow" (Communications Toolbox Support Package for Xilinx Zynq-Based Radio)

- "Hardware-Software Co-Design Workflow" (Communications Toolbox Support Package for Xilinx Zynq-Based Radio)

- "LTE HDL MIB Recovery" on page 5-92

- "LTE HDL SIB1 Recovery" on page 5-74

# **Reference Page Examples**

# **Append CRC Checksum to Streaming Data**

This example shows how to use the LTE CRC Encoder block to encode data, and how to compare the hardware-friendly design with the results from LTE Toolbox<sup>m</sup>. The workflow follows these steps:

- **1** Generate frames of random input samples in MATLAB.

- 2 Generate and append a CRC checksum using the LTE Toolbox function lteCRCEncode.

- 3 Convert framed input data to a stream of samples and import the stream into Simulink®.

- 4 To encode the samples using a hardware-friendly architecture, run the Simulink model, which contains the Wireless HDL Toolbox<sup>™</sup> block LTE CRC Encoder.

- 5 Export the stream of bits, which now has an appended CRC checksum, to the MATLAB® workspace.

- **6** Convert the sample stream back to framed data, and compare the frames with the reference frames and checksum.

Generate input data frames. Generate reference output data using lteCRCEncode.

```

frameLength = 256;

numframes = 2;

rng(0);

txframes = cell(1,numframes);

txcodeword = cell(1,numframes);

rxSoftframes = cell(1,numframes);

for ii = 1:numframes

txframes{ii} = randi([0 1],frameLength,1)>0.5;

CRCType = '24B';

CRCMask = 50;

txcodeword{ii} = lteCRCEncode(txframes{ii},CRCType,CRCMask);

```

#### end

Serialize input data for the Simulink model. Leave enough time between frames for each frame to be fully encoded before the next one starts. For CRC 24 encoding, the checksum adds 24 parity bits at the end of the frame. The hardware-friendly algorithm also adds *CRCLength* + 3 cycles of latency.

```

idleCyclesBetweenSamples = 0;

idleCyclesBetweenFrames = 24+27;

outputSize = 1;

[sampleIn,ctrlIn] = whdlFramesToSamples(...

txframes,idleCyclesBetweenSamples,idleCyclesBetweenFrames,outputSize);

```

Run the Simulink model.

```

sampletime = 1;

simTime = length(ctrlIn);

modelname = 'ltehdlCRCEncoderModel';

open(modelname);

sim(modelname);

```

The Simulink model exports sampleOut and ctrlOut back to the MATLAB workspace. Deserialize the output samples, and compare the framed data to the reference data.

```

txhdlframes = whdlSamplesToFrames(sampleOut,ctrlOut);

```

Maximum frame size computed to be 280 samples.

LTE CRC Encoder Frame 1: Behavioral and HDL simulation differ by 0 bits Frame 2: Behavioral and HDL simulation differ by 0 bits

#### See Also

Blocks LTE CRC Encoder

#### Functions lteCRCEncode

LTECKCEncode

#### **More About**

"Check for CRC Errors in Streaming Samples" on page 3-4

# **Check for CRC Errors in Streaming Samples**

This example shows how to use the LTE CRC Decoder block to check encoded data, and how to compare the hardware-friendly design with the results from LTE Toolbox<sup>TM</sup>. The workflow follows these steps:

- **1** Generate frames of random input samples in MATLAB.

- 2 Generate and append the CRC checksum using the LTE Toolbox function lteCRCEncode.

- 3 Convert framed input data and checksum to a stream of samples and import it to Simulink®.

- 4 To check the samples against the checksum using a hardware-friendly architecture, run the Simulink model. The model contains the Wireless HDL Toolbox<sup>™</sup> block LTE CRC Decoder.

- **5** Export the stream of samples back to the MATLAB® workspace.

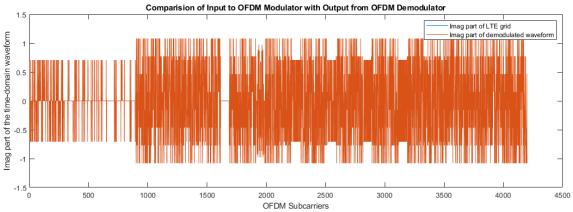

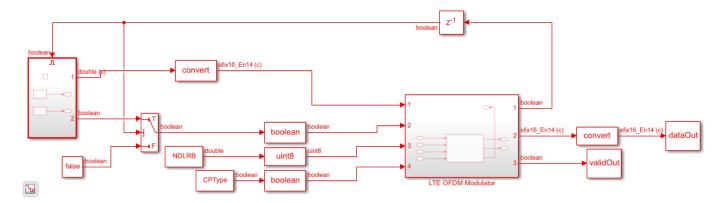

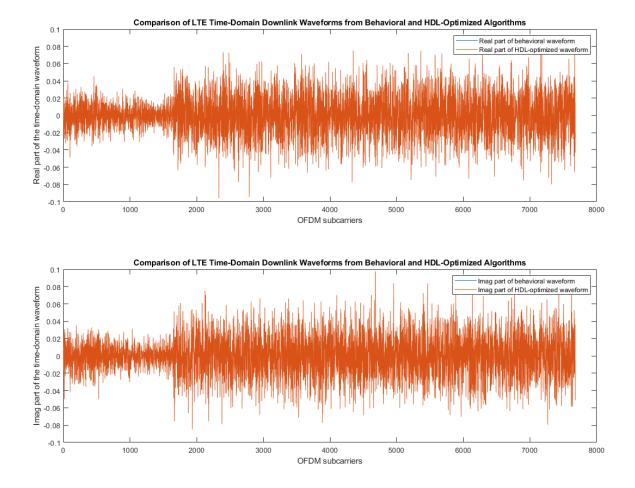

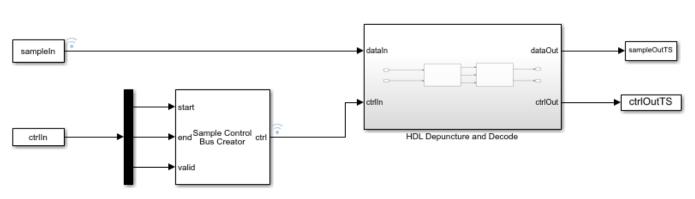

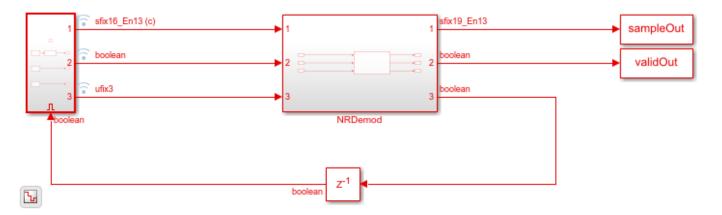

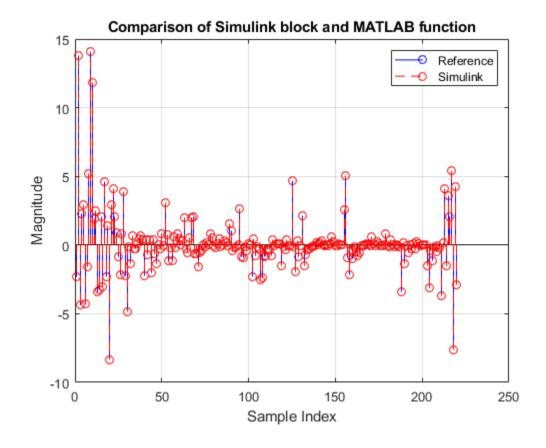

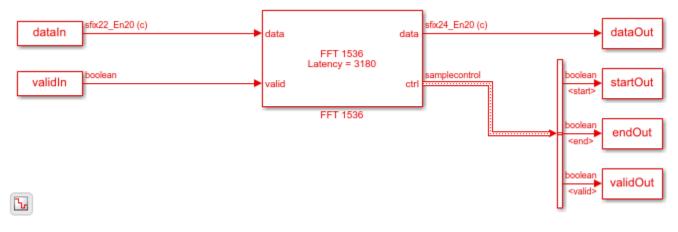

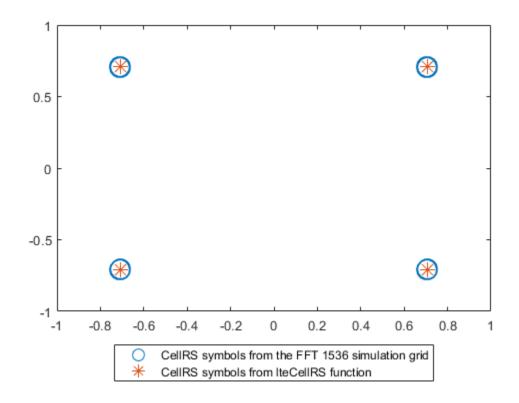

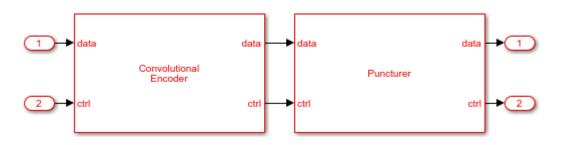

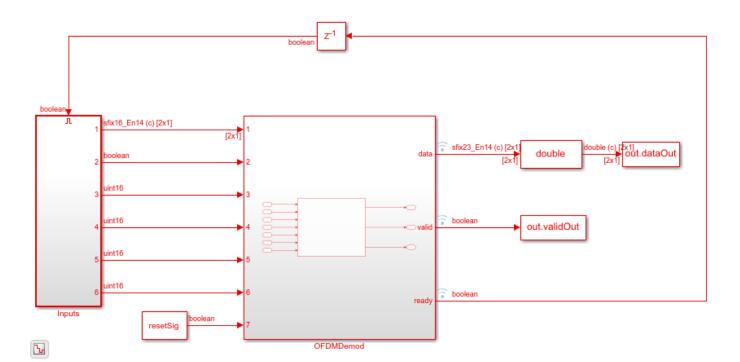

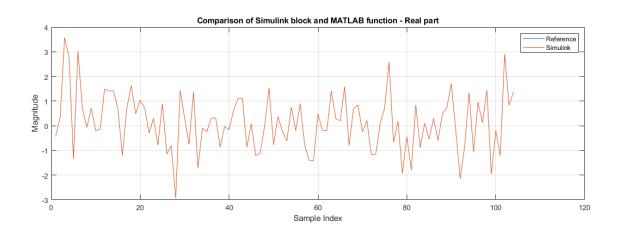

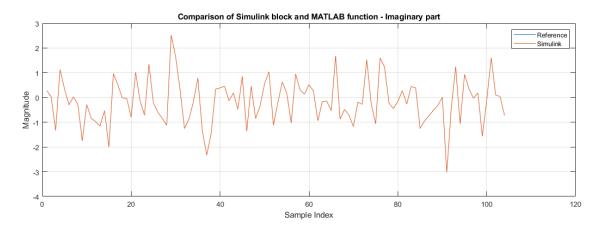

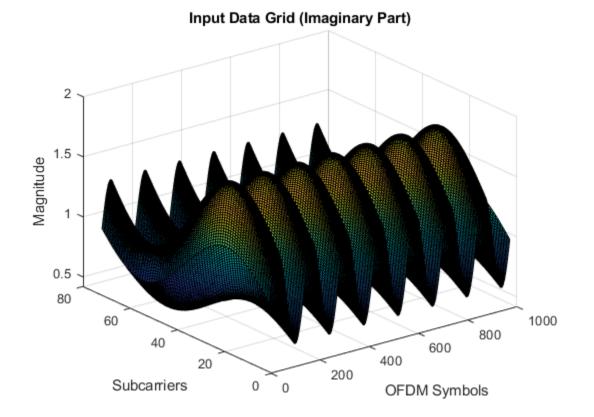

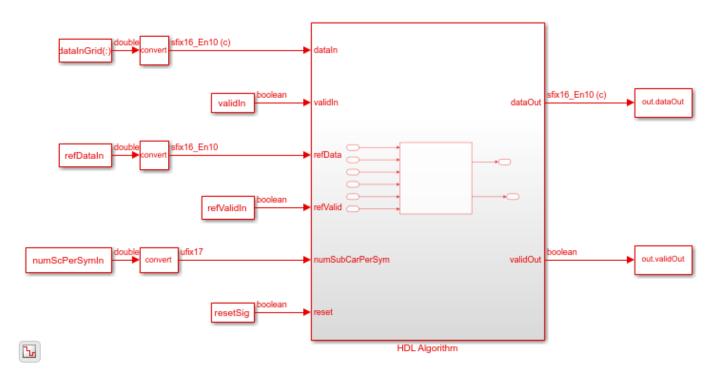

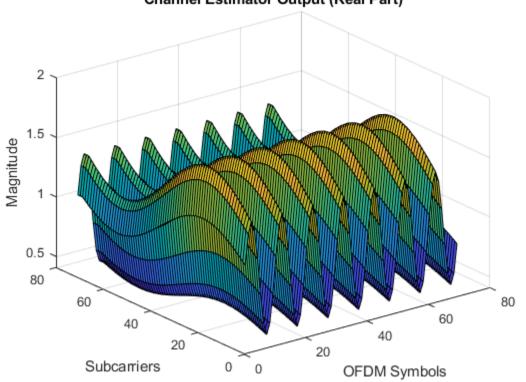

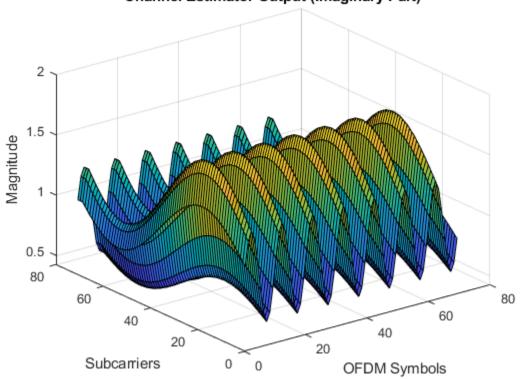

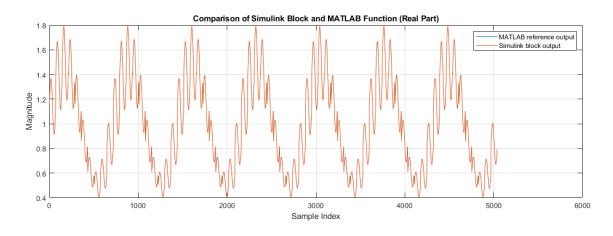

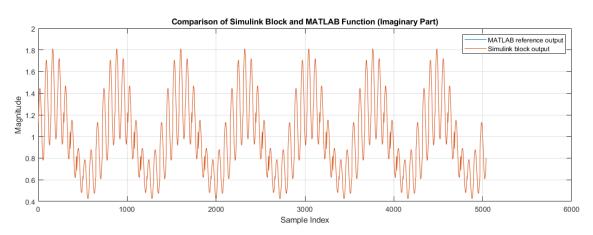

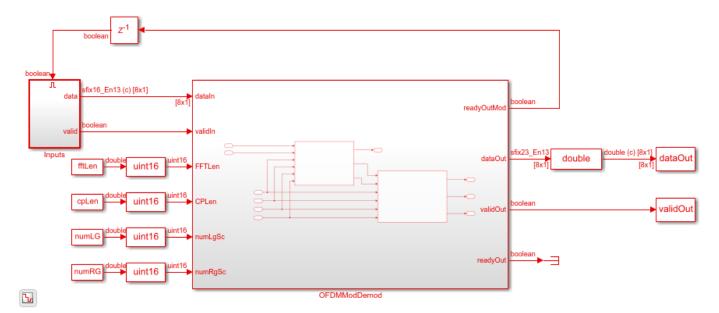

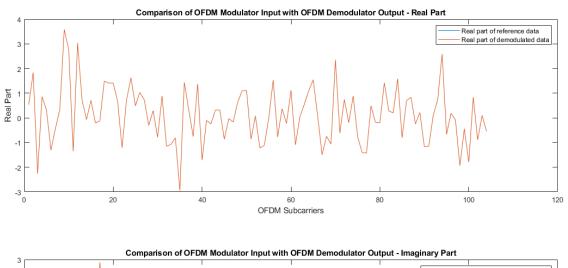

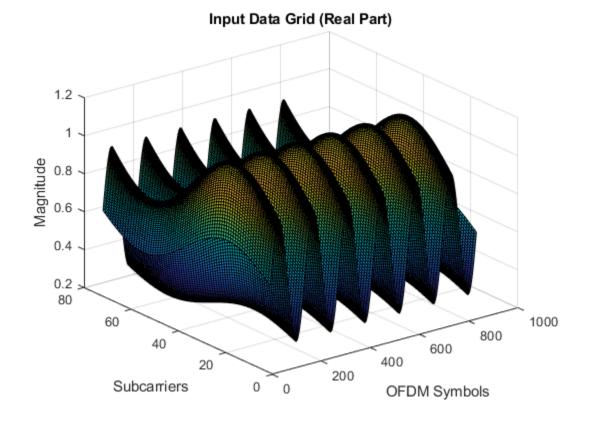

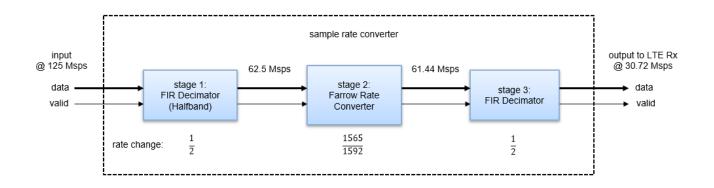

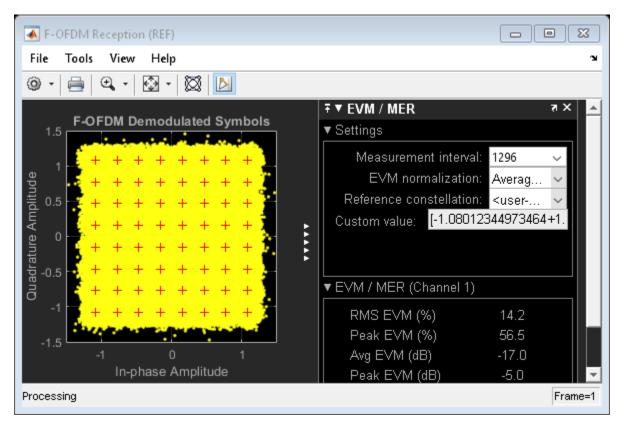

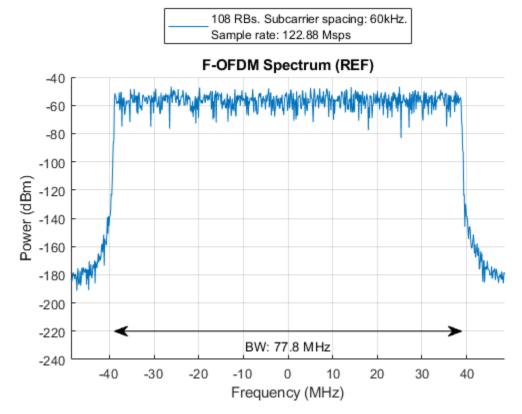

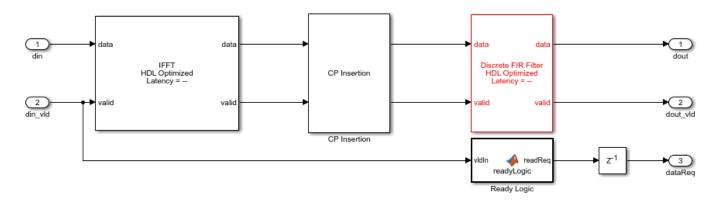

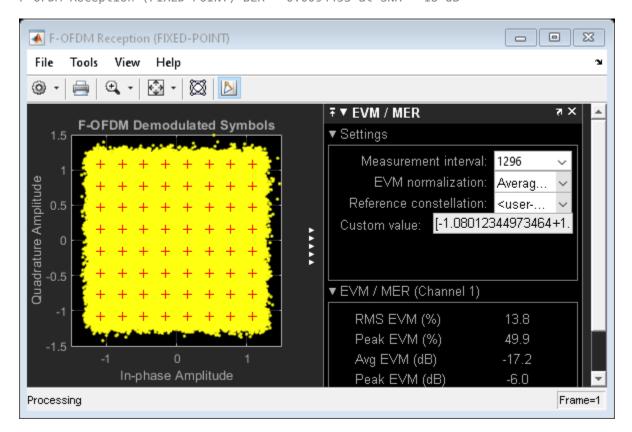

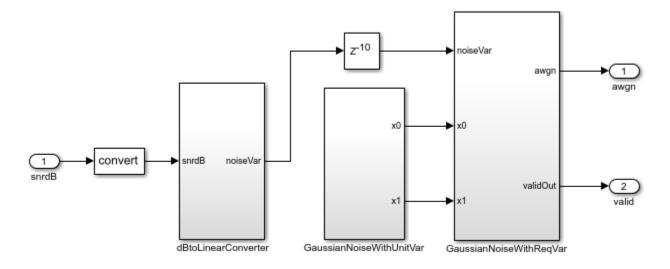

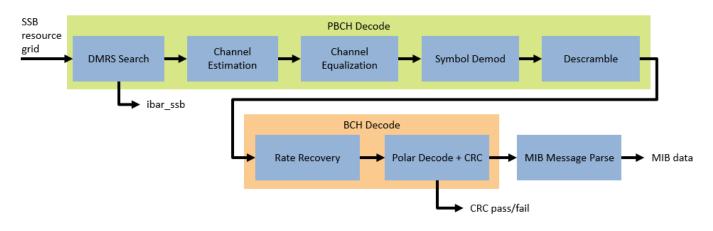

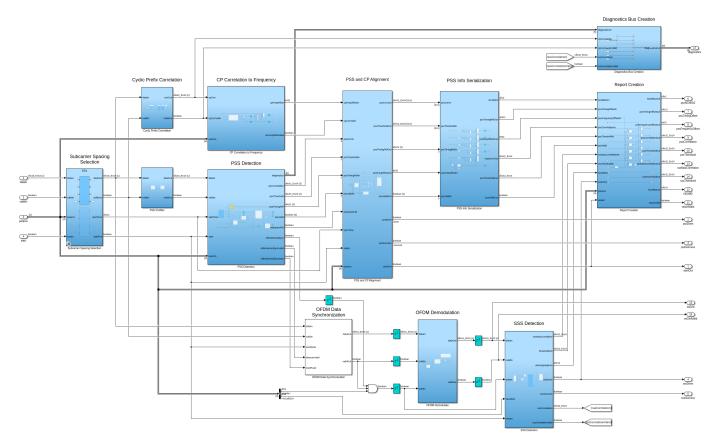

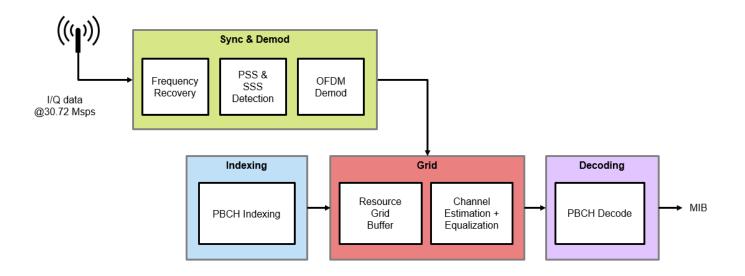

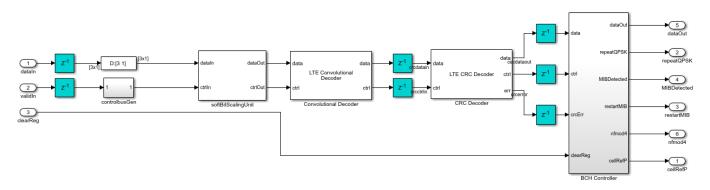

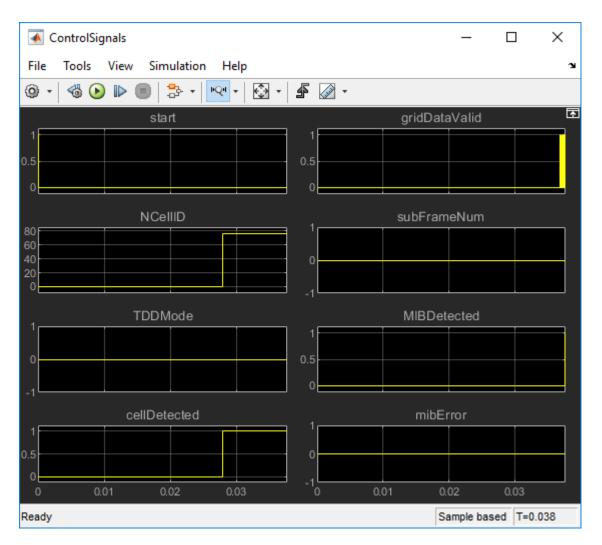

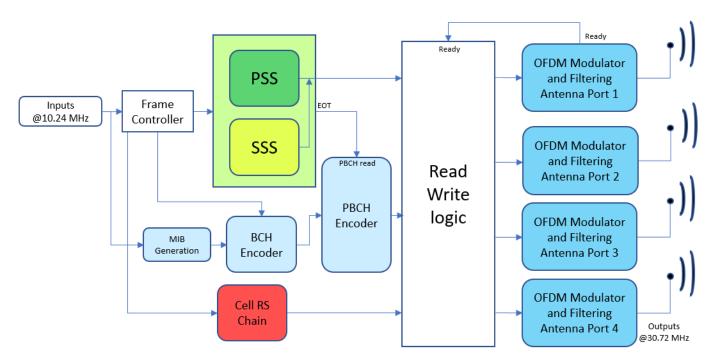

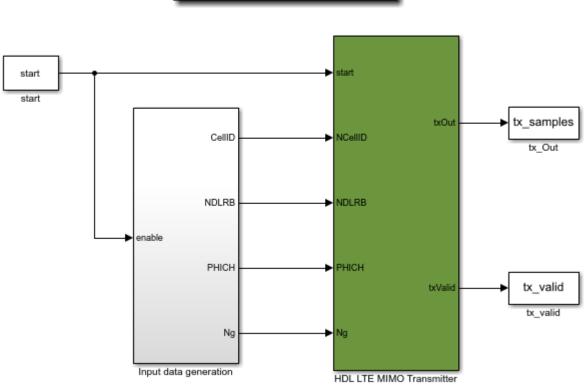

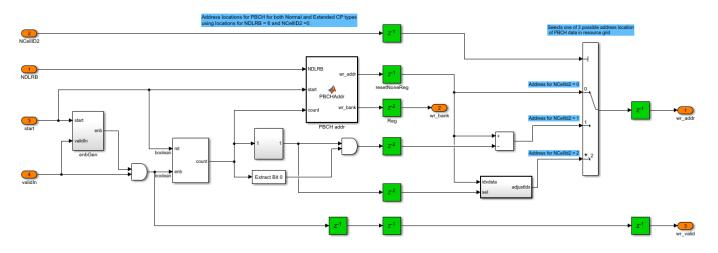

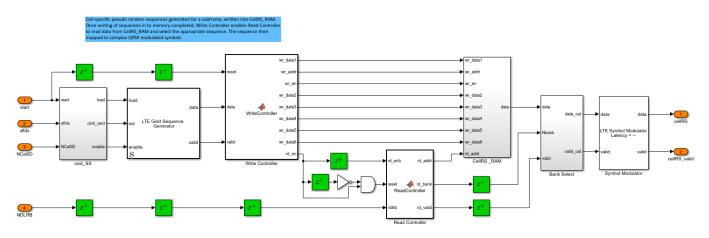

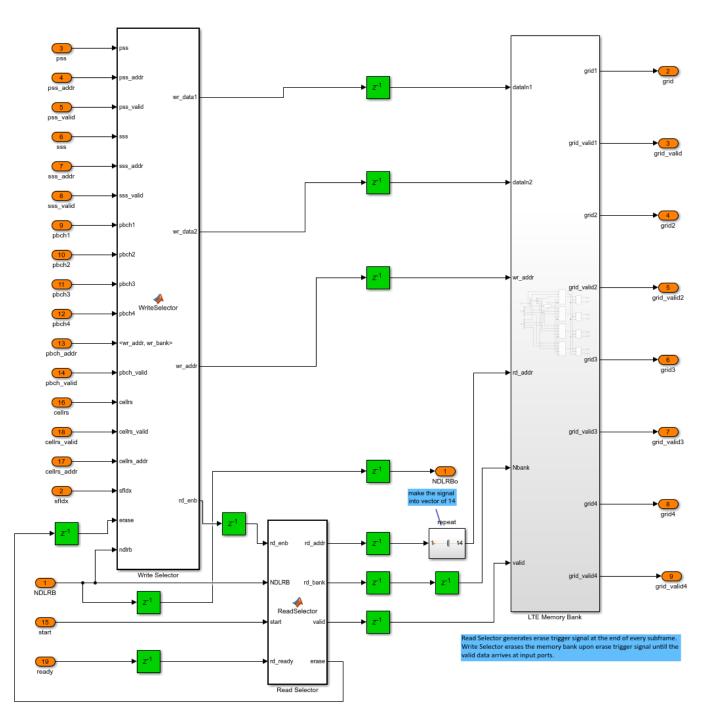

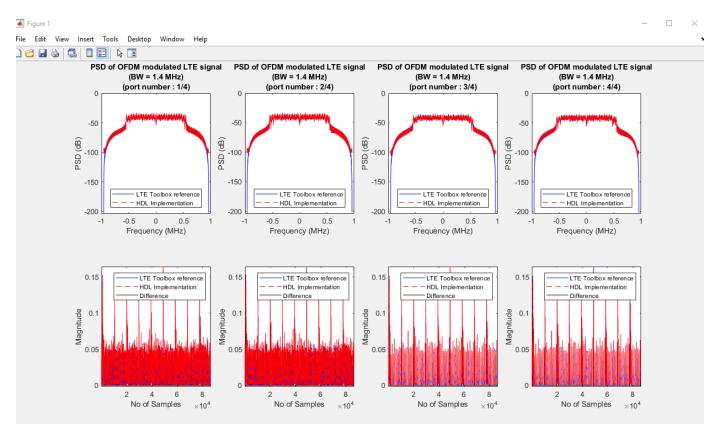

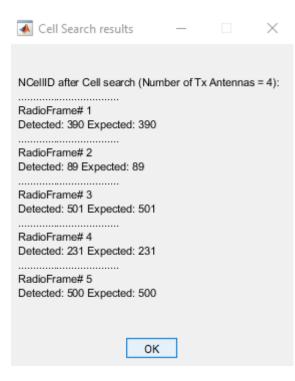

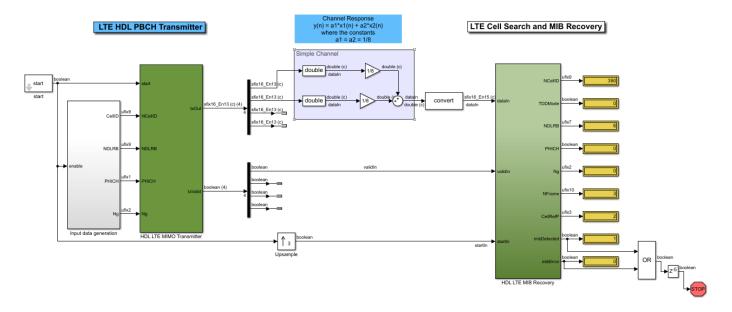

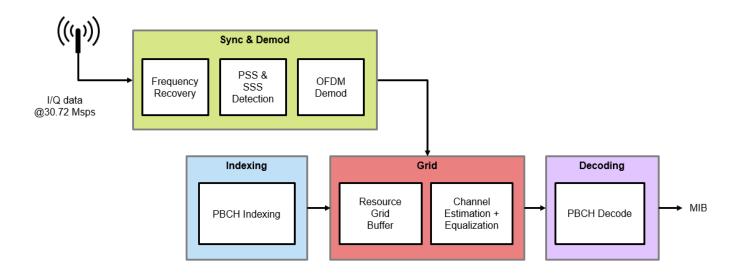

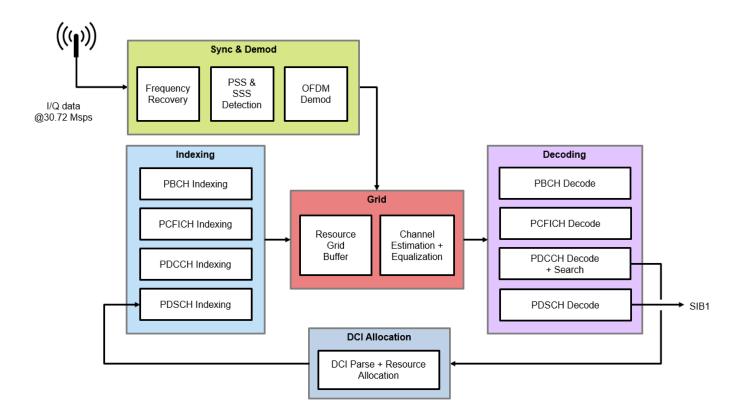

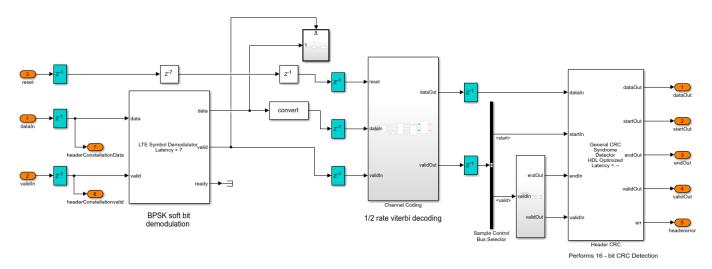

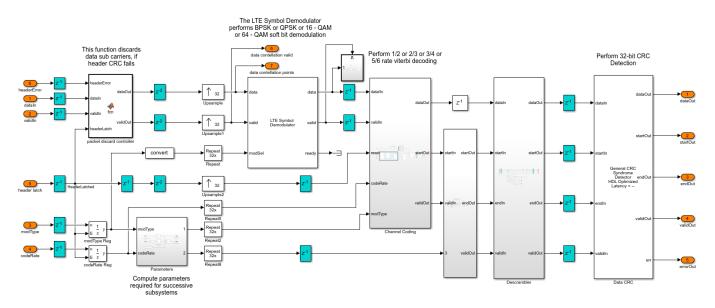

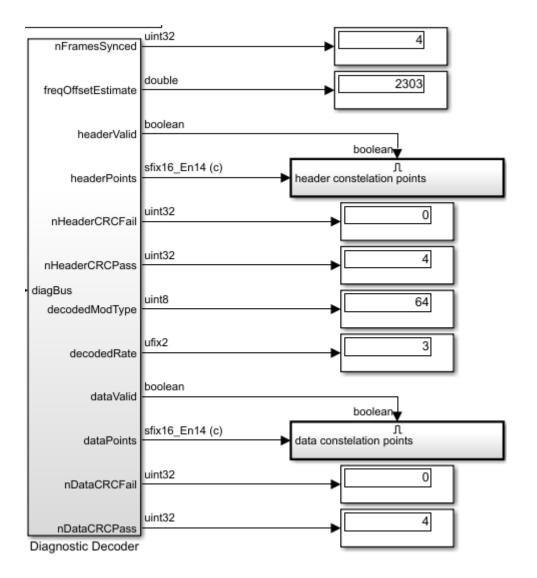

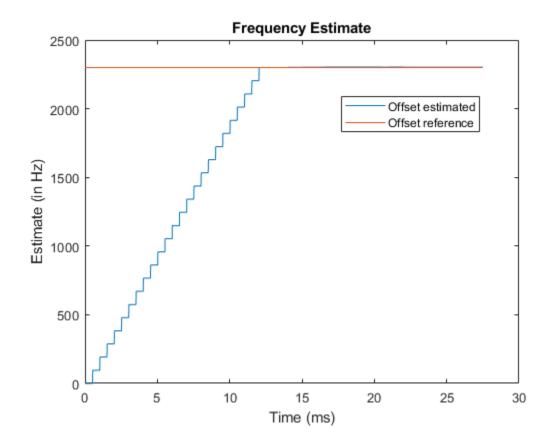

- **6** Convert the sample stream back to framed data, and compare the frames with the reference data.